Design Guide

93

Intel

®

82870P2 (P64H2)

Intel

®

82870P2 (P64H2)

8

The 82870P2 (P64H2) is a peripheral chip that performs PCI/PCI-X bridging functions between

Hub Interface and the PCI bus. The P64H2 is an integral part of the E7500 chipset, bridging the

MCH and the PCI/PCI-X bus. On the primary bus, the P64H2 utilizes a 16-bit data bus to interface

with the Hub Interface 2.0, and on the secondary bus, it supports two 64-bit PCI bus segments.

Either of the secondary PCI/PCI-X bus interfaces can be configured to operate in PCI or PCI-X

mode. Each PCI/PCI-X interface contains an I/OxAPIC with 24 interrupts and a hot plug controller

that supports each PCI/PCI-X bus segment.

8.1

PCI/PCI-X Design Guidelines

The P64H2 contains two PCI/PCI-X Interfaces. The PCI Interface has a 33/66 MHz bus speed, and

the PCI-X interface has a 66/100/133 MHz bus speed (see

NOTE:

Frequencies specified are not the only ones supported, rather the maximum allowed in the

configuration.

Intel simulated the PCI/PCI-X bus topologies shown in

. If a

platform implements a PCI/PCI-X topology not found in the following sections, it is the

responsibility of the system designer to ensure the system meets the specified timings. The

recommended lengths specified are not intended to replace thorough system simulations and

validation.

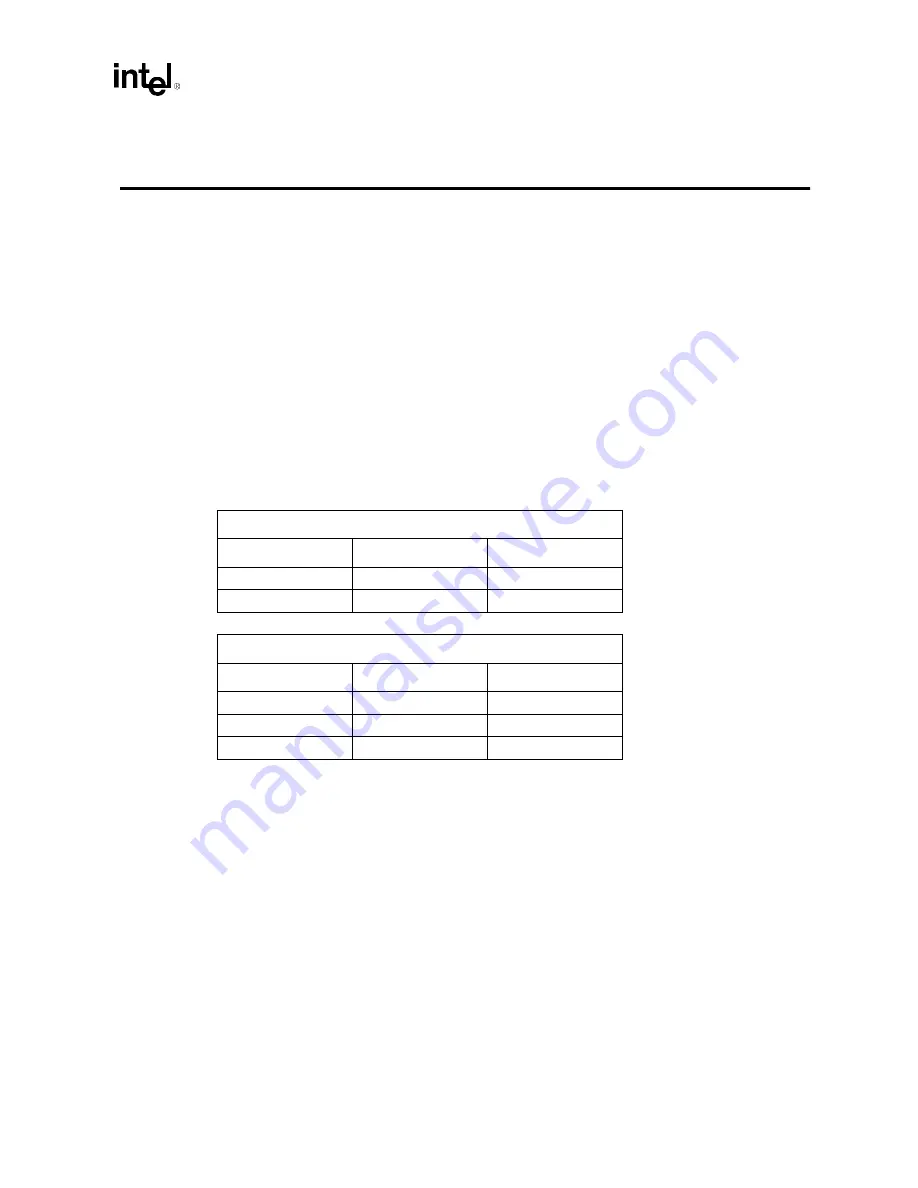

Table 8-1. PCI/PCI-X Frequencies

PCI

Frequency

Maximum Slots

Voltage

33 MHz

6

3.3 V, 5 V

66 MHz

2

3.3 V

PCI-X

Frequency

Maximum Slots

Voltage

66 MHz

4

3.3 V

100 MHz

2

3.3 V

133 MHz

1

3.3 V

Summary of Contents for Xeon

Page 24: ...Introduction 24 Design Guide This page is intentionally left blank ...

Page 30: ...Component Quadrant Layout 30 Design Guide This page is intentionally left blank ...

Page 52: ...Platform Clock Routing Guidelines 52 Design Guide This page is intentionally left blank ...

Page 66: ...System Bus Routing Guidelines 66 Design Guide This page is intentionally left blank ...

Page 118: ...Intel 82870P2 P64H2 118 Design Guide This page is intentionally left blank ...

Page 146: ...I O Controller Hub 146 Design Guide This page is intentionally left blank ...

Page 148: ...Debug Port 148 Design Guide This page is intentionally left blank ...

Page 210: ...Schematic Checklist 210 Design Guide This page is intentionally left blank ...

Page 220: ...Layout Checklist 220 Design Guide This page is intentionally left blank ...

Page 222: ...Schematics 222 Design Guide This page is intentionally left blank ...