Developer’s Manual

January, 2004

103

Intel XScale® Core

Developer’s Manual

Performance Monitoring

8.2.2

Performance Count Registers (PMN0 - PMN1; CP14 -

Register 2 and 3, Respectively)

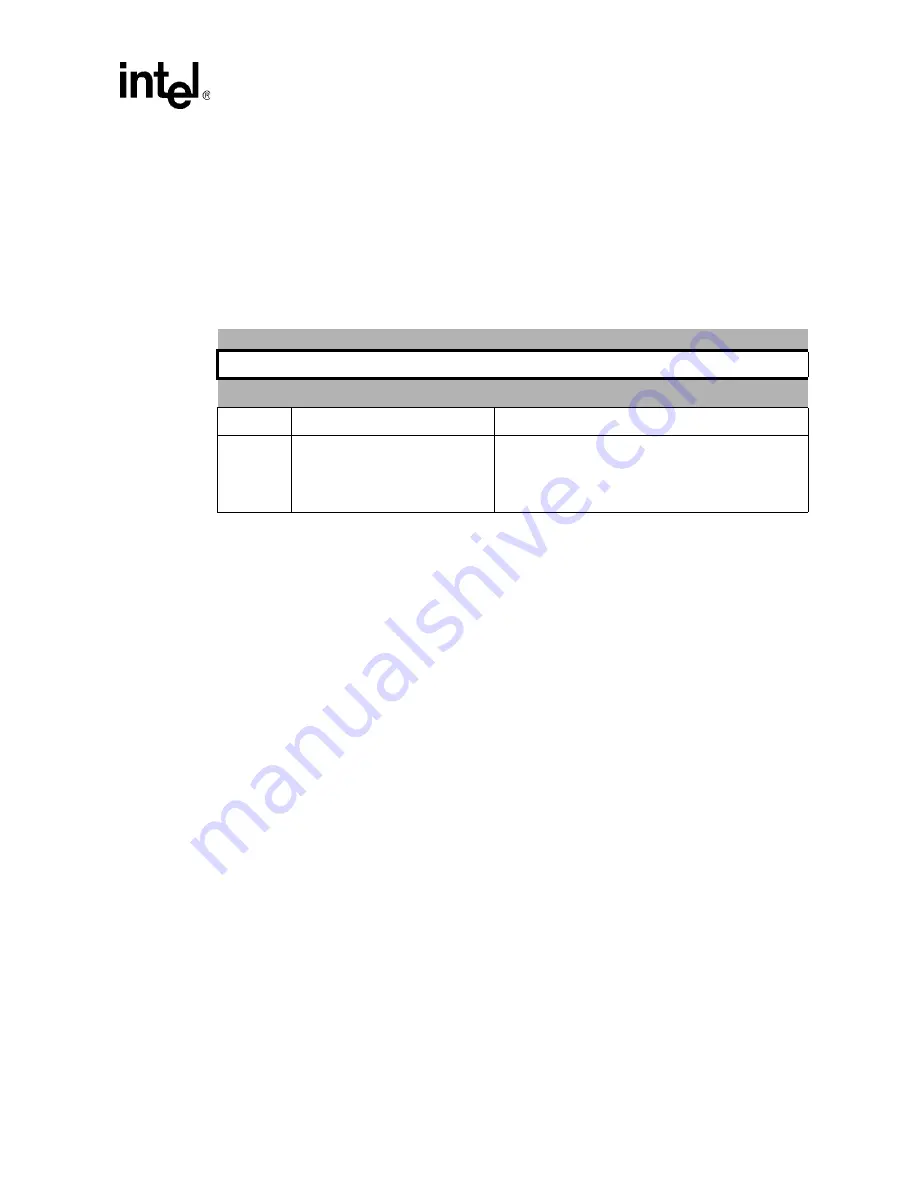

There are two 32-bit event counters; their format is shown in

Table 8-7

. The event counters are

reset to ‘0’ by the PMNC register or can be set to a predetermined value by directly writing to

them. When an event counter reaches its maximum value 0xFFFF,FFFF, the next event it needs to

count will cause it to roll over to zero and set the overflow flag (bit 8 or 9) in PMNC. An IRQ or

FIQ interrupt will be reported if it is enabled via bit 4 or 5 in the PMNC register.

8.2.3

Extending Count Duration Beyond 32 Bits

To increase the monitoring duration, software can extend the count duration beyond 32 bits by

counting the number of overflow interrupts each 32-bit counter generates. This can be done in the

interrupt service routine (ISR) where an increment to some memory location every time the

interrupt occurs will enable longer durations of performance monitoring. This does intrude upon

program execution but is negligible, since the ISR execution time is in the order of tens of cycles

compared to the number of cycles it took to generate an overflow interrupt (2

32

).

8.2.4

Performance Monitor Control Register (PMNC)

The performance monitor control register (PMNC) is a coprocessor register that:

•

controls which events PMN0 and PMN1 will monitor

•

detects which counter overflowed

•

enables/disables interrupt reporting

•

extends CCNT counting by six more bits (cycles between counter rollover = 2

38

)

•

resets all counters to zero

•

and enables the entire mechanism

Table 8-8

shows the format of the PMNC register.

Table 8-3.

Performance Monitor Count Register (PMN0 and PMN1)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

Event Counter

reset value: unpredictable

Bits

Access

Description

31:0

Read / Write

32-bit event counter

- Reset to ‘0’ by PMNC register.

When an event counter reaches its maximum value

0xFFFF,FFFF, the next event it needs to count will cause

it to roll over to zero and generate an IRQ interrupt if

enabled.