110

January, 2004

Developer’s Manual

Intel XScale® Core

Developer’s Manual

Performance Monitoring

8.3.5

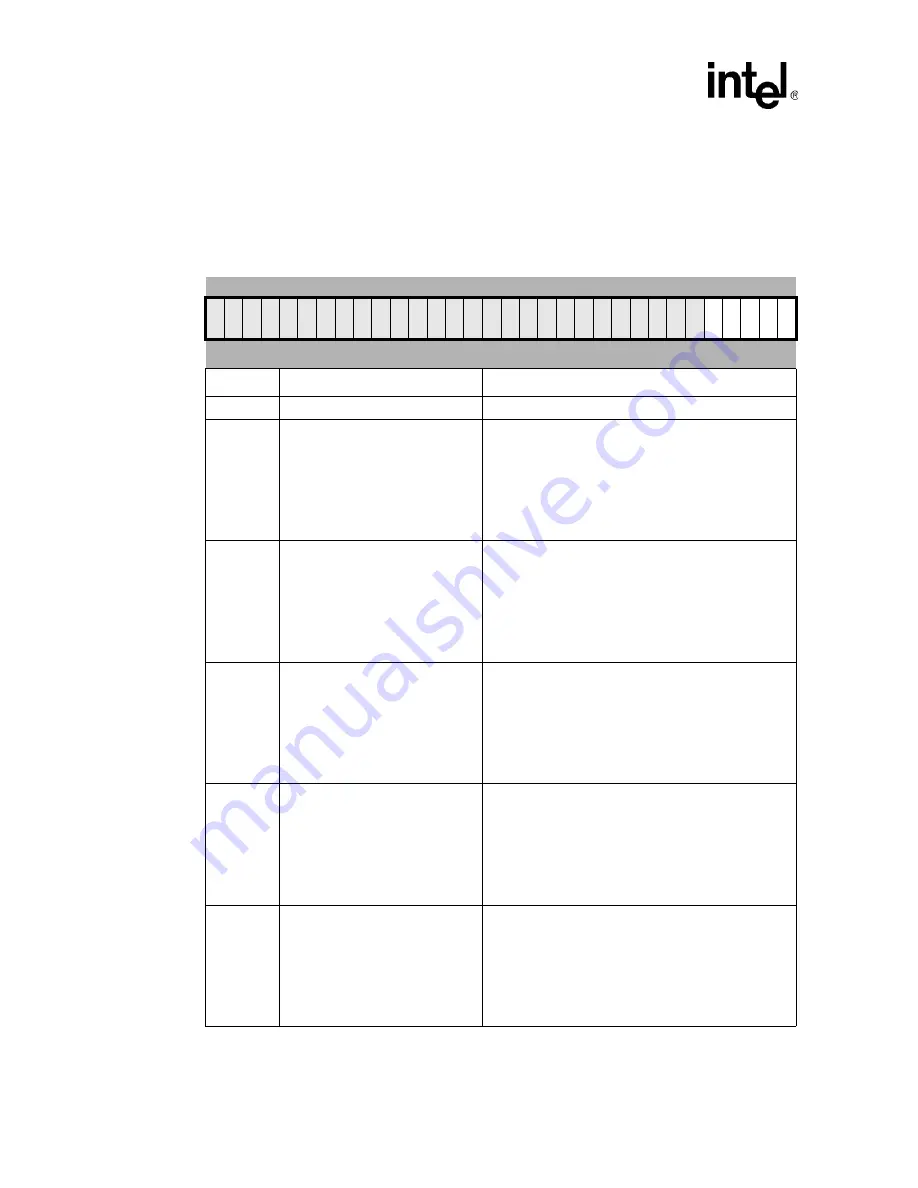

Overflow Flag Status Register (FLAG)

FLAG identifies which counter has overflowed and also indicates an interrupt has been requested if

the overflowing counter’s corresponding interrupt enable bit (contained within INTEN) is asserted.

An overflow is cleared by writing a ‘1’ to the overflow bit.

Table 8-10.

Overflow Flag Status Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9

8

7

6

5

4

3

2

1

0

P

3

P

2

P

1

P

0

C

reset value:

[4:0] = 0b00000

, others unpredictable

Bits

Access

Description

31:5

Read-unpredictable / Write-as-0

Reserved

4

Read / Write

PMN3 Overflow Flag (P3)

-

Read Values:

0 = no overflow

1 = overflow has occurred

Write Values:

0 = no change

1 = clear this bit

3

Read / Write

PMN2 Overflow Flag (P2)

-

Read Values:

0 = no overflow

1 = overflow has occurred

Write Values:

0 = no change

1 = clear this bit

2

Read / Write

PMN1 Overflow Flag (P1)

-

Read Values:

0 = no overflow

1 = overflow has occurred

Write Values:

0 = no change

1 = clear this bit

1

Read / Write

PMN0 Overflow Flag (P0)

-

Read Values:

0 = no overflow

1 = overflow has occurred

Write Values:

0 = no change

1 = clear this bit

0

Read / Write

CCNT Overflow Flag (C)

-

Read Values:

0 = no overflow

1 = overflow has occurred

Write Values:

0 = no change

1 = clear this bit