168

January, 2004

Developer’s Manual

Intel XScale® Core

Developer’s Manual

Performance Considerations

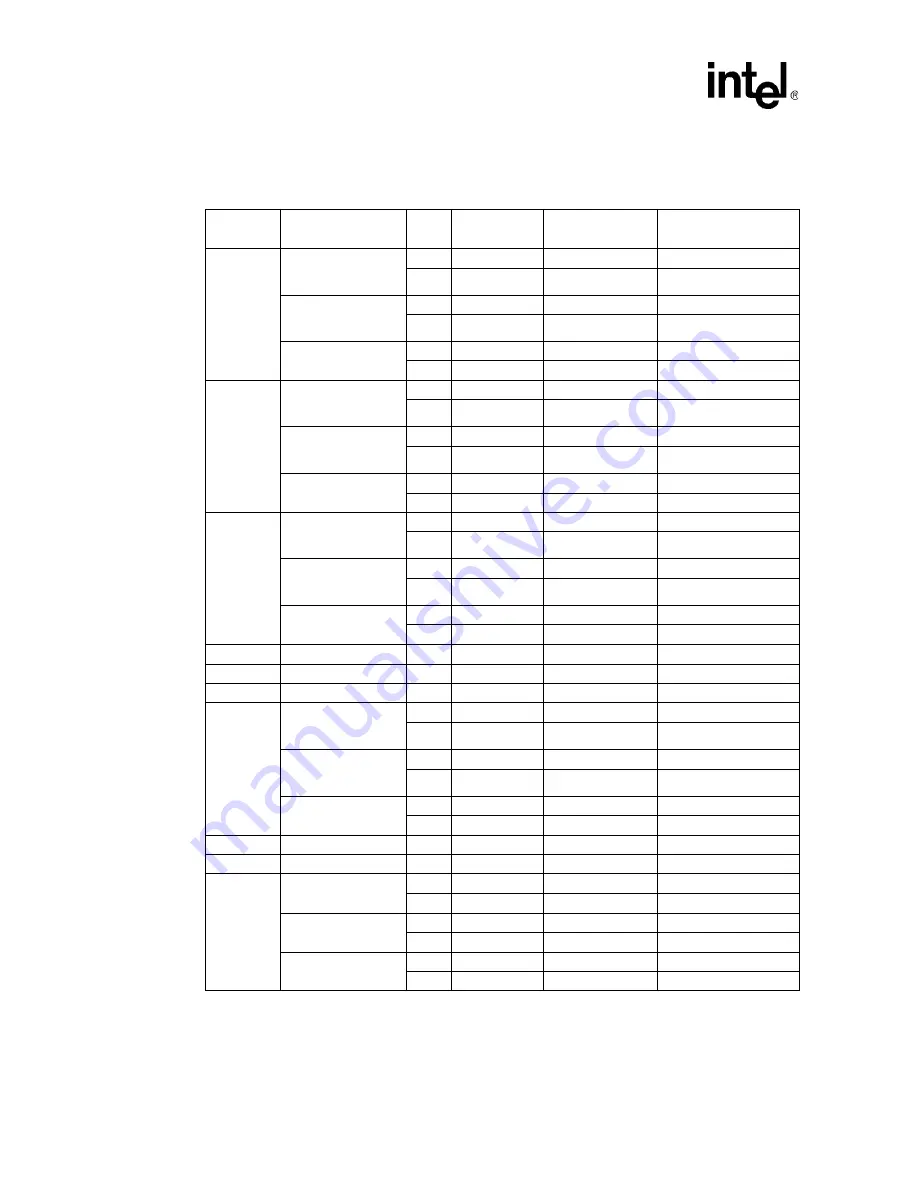

10.4.4

Multiply Instruction Timings

Table 10-6.

Multiply Instruction Timings (Sheet 1 of 2)

Mnemonic

Rs Value

(Early Termination)

S-Bit

Value

Minimum

Issue Latency

Minimum Result

Latency

a

Minimum Resource

Latency (Throughput)

MLA

Rs[31:15] = 0x00000

or

Rs[31:15] = 0x1FFFF

0

1

2

1

1

2

2

2

Rs[31:27] = 0x00

or

Rs[31:27] = 0x1F

0

1

3

2

1

3

3

3

all others

0

1

4

3

1

4

4

4

MUL

Rs[31:15] = 0x00000

or

Rs[31:15] = 0x1FFFF

0

1

2

1

1

2

2

2

Rs[31:27] = 0x00

or

Rs[31:27] = 0x1F

0

1

3

2

1

3

3

3

all others

0

1

4

3

1

4

4

4

SMLAL

Rs[31:15] = 0x00000

or

Rs[31:15] = 0x1FFFF

0

2

RdLo = 2; RdHi = 3

2

1

3

3

3

Rs[31:27] = 0x00

or

Rs[31:27] = 0x1F

0

2

RdLo = 3; RdHi = 4

3

1

4

4

4

all others

0

2

RdLo = 4; RdHi = 5

4

1

5

5

5

SMLALxy

N/A

N/A

2

RdLo = 2; RdHi = 3

2

SMLAWy

N/A

N/A

1

3

2

SMLAxy

N/A

N/A

1

2

1

SMULL

Rs[31:15] = 0x00000

or

Rs[31:15] = 0x1FFFF

0

1

RdLo = 2; RdHi = 3

2

1

3

3

3

Rs[31:27] = 0x00

or

Rs[31:27] = 0x1F

0

1

RdLo = 3; RdHi = 4

3

1

4

4

4

all others

0

1

RdLo = 4; RdHi = 5

4

1

5

5

5

SMULWy

N/A

N/A

1

3

2

SMULxy

N/A

N/A

1

2

1

UMLAL

Rs[31:15] = 0x00000

0

2

RdLo = 2; RdHi = 3

2

1

3

3

3

Rs[31:27] = 0x00

0

2

RdLo = 3; RdHi = 4

3

1

4

4

4

all others

0

2

RdLo = 4; RdHi = 5

4

1

5

5

5