SECTION 7

System Information

PEN*KEY

R

6200/6300 Hand-Held Computer Programmer’s Reference Guide 7-13

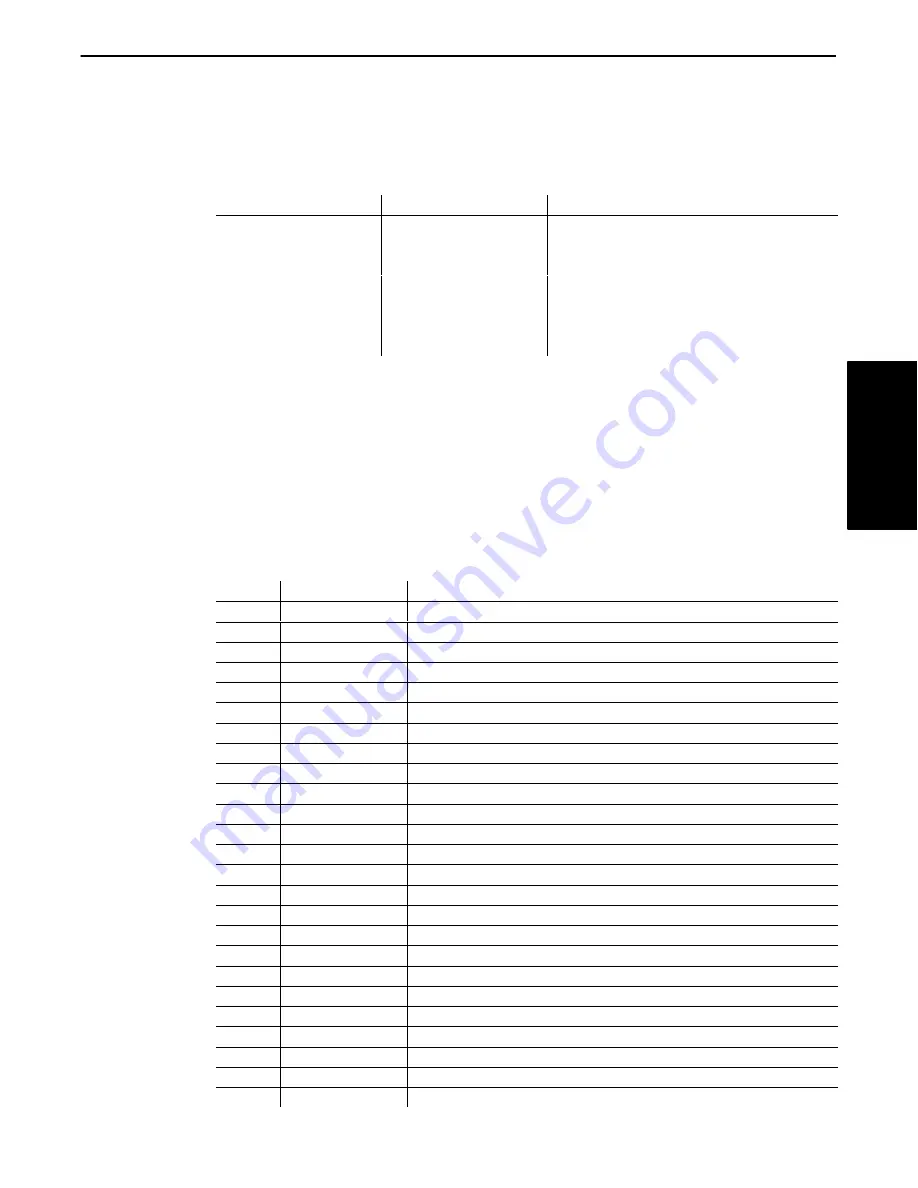

COM1 Pin-Outs

Table 7Ć5

COM1 Connector Pin-Outs

9Ćpin Connector

25Ćpin Connector

Description

2

2

TX

3

3

RX

5

7

SG

7

4

RTS

8

5

CTS

4

20

DTR

(see Note below)

6

6

DSR

(see Note below)

"

NOTE:

DTR is looped back to DSR, both at dock and at internal UART. This means there is no DTR

or DSR connection from the UART to the modem.

Hardware Interrupts

The system supports the following hardware interrupts:

Table 7Ć6

Hardware Interrupt Definitions

Vector Type

Usage

00h

Processor

Divide error

01h

Processor

Debug exceptions (e.g., single step)

02h

Processor

Nonmaskable interrupt

03h

Processor

Breakpoint

04h

Processor

Overflow trap

05h

Processor

Bounds exception

07h

Processor

Invalid opcode

08h

IRQ0; Processor Timer interrupt handler; Double exception

09h

IRQ1; Processor Keyboard interrupt handler; Coprocessor segment overrun

0Ah

IRQ2; Processor Slave (cascades IRQ8 Ċ IRQ15); Invalid task state segment

0Bh

IRQ3; Processor Serial port 2 (i.e., COM2:); Segment not present

0Ch

IRQ4; Processor Serial port 1 (i.e., COM1:); Stack fault

0Dh

IRQ5; Processor Internal bar code scanner; General protection error

0Eh

IRQ6; Processor Reserved for PC Card Ċ (card status change); Page fault

0Fh

IRQ7

AND PLNET ć ISA (embedded hardware)

10h

Processor

Coprocessor error

70h

IRQ8

RealĆtime clock periodic interrupt

71h

IRQ9

Reserved for H8 OBF INTERRUPT and PC Card

72h

IRQ10

Reserved for PC Card (modem, COM3:)

73h

IRQ11

Reserved for PC Card (modem, COM4:)

74h

IRQ12

Touch screen digitizer

75h

IRQ13

Reserved for PC Card

76h

IRQ14

Reserved for PC Card

77h

IRQ15

H8 system interrupt

SMI

System management interrupt

7. System Information