Open-Q™ 845 µSOM Development Kit User Guide

Version 1.0

© Copyright Intrinsyc Technologies Corporation

28 of 30

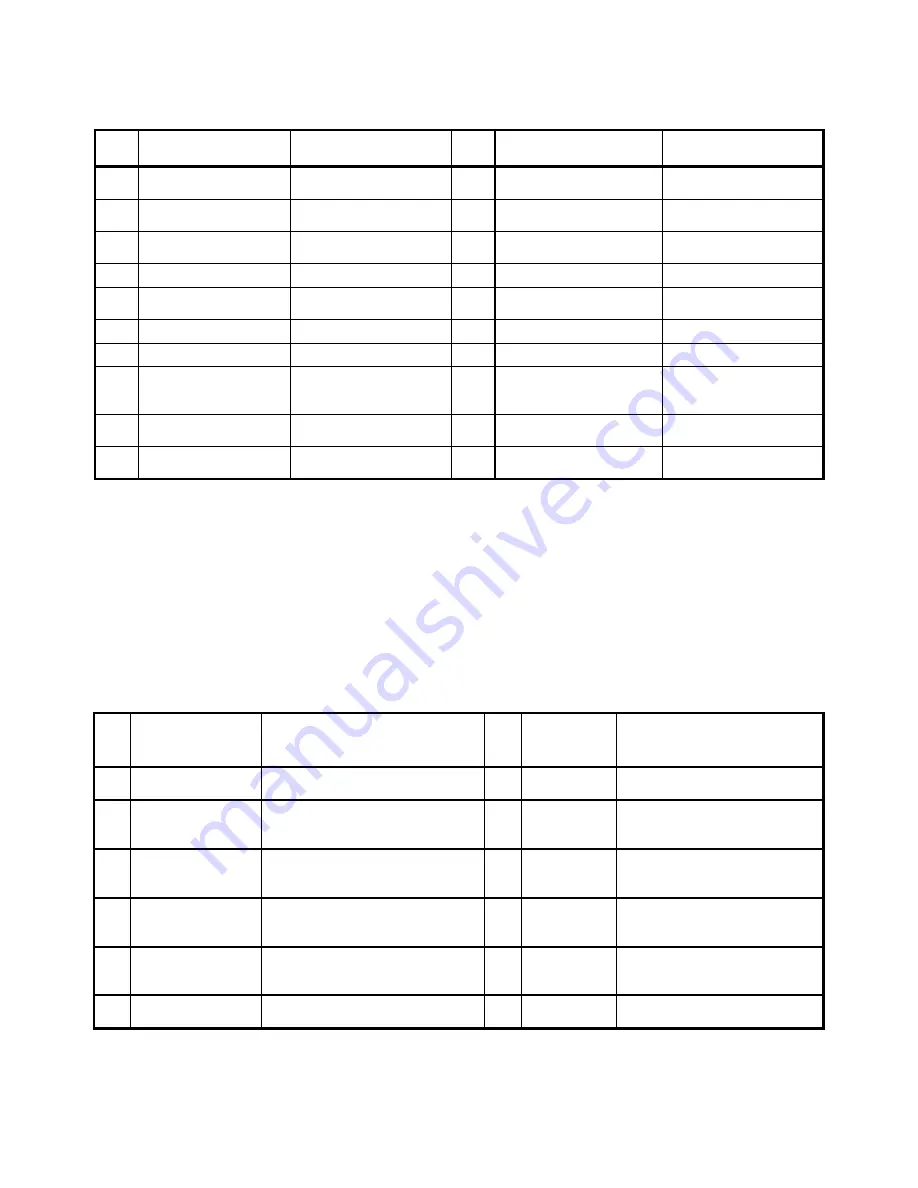

Table 14. Audio Outputs Expansion Header Pinout J1901

Pin

No

Signal

Description

Pin

No

Signal

Description

1

CDC_LINE_OUT1_P

Codec Line Out 1 Positive

2

CDC_LINE_OUT1_N

Codec Line Out 1

Negative

3

CDC_LINE_OUT2_P

Codec Line Out 2 Positive

4

CDC_LINE_OUT2_N

Codec Line Out 2

Negative

5

CDC_LINE_REF

Codec Reference (GND)

6

MB_VREG_3P3

Carrier board switching

reg3.3V

7

GND

System Ground

8

GND

System Ground

9

CDC_EAR_P

Earphone Amplifier

Output Positive

10

CDC_EAR_N

Earphone Amplifier

Output Negative

11

GND

System Ground

12

SOM_SYS_PWR_PER

SOM System Power

13

CDC_SWR_CLK

Codec PDM Clock

14

CDC_SWR_DATA

Codec PDM Data

15

CDC_WSA_EN

Codec GPIO, can be used

as Speaker Amp Enable 1

16

PMI8998_SPKR_AMP_E

N2

µSOM PMIC GPIO11,

can be used as Speaker

Amp Enable 2

17

VREG_S4A_1P8

µSOM LDO Regulator

S4A +1.8V

18

DC_IN_12V

Voltage from DC Power

Input +12.0V

19

MB_VREG_5P0

Carrier board switching

reg5.0V

20

GND

System Ground

For more details regarding configuring the GPIOs on this header, refer to the Open-Q 845 Software

Release Notes to determine feature support in the latest software release.

3.7.20

Audio IO Expansion Header J2000 (10)

In addition to the Qualcomm Audio Codec WCD9340 (28), the Open-Q 845 µSOM Development

Kit also includes other digital audio interfaces. The Audio IO Expansion Header J2000 exposes some

of these interfaces for the user. See item 10 in Figure 1 for the carrier board location of this header.

The pinout for this header is shown in the table below.

Table 15. Audio IO Expansion Header Pinout J2000

Pi

n

No

Signal

Description

Pi

n

No

Signal

Description

1

GPIO57_FORCE_U

SB_BOOT

CPU GPIO57 – can be configured as

QUA_MI2S_MCLK

2

GND

Ground

3

GPIO58_QUA_MI2

S_SCK

CPU GPIO58 – can be configured as

QUA_MI2S_SCK

4

GPIO61_QU

A_MI2S_DA

TA1

CPU GPIO61 – can be configured

as QUA_MI2S_DATA1

5

GPIO59_QUA_MI2

S_WS

CPU GPIO59 – can be configured as

QUA_MI2S_WS

6

GPIO62_QU

A_MI2S_DA

TA2

CPU GPIO62 – can be configured

as QUA_MI2S_DATA2

7

GPIO60_QUA_MI2

S_DATA0

CPU GPIO60 – can be configured as

QUA_MI2S_DATA0

8

GPIO63_QU

A_MI2S_DA

TA3

CPU GPIO63 – can be configured

as QUA_MI2S_DATA3

9

GND

Ground

10

GPIO64_CO

DEC_RST_N

CPU GPIO64 – can be configured

as PRI_MI2S_MCLK (see Note 1

below)

11

GPIO65_CODEC_S

PI_MISO

CPU GPIO65 – can be configured as

PRI_MI2S_SCK (see Note 1 below)

12

GND

Ground