www.irf.com

Page 27 of 50

IRAUDAMP5 REV 3.1

+

-

.

.

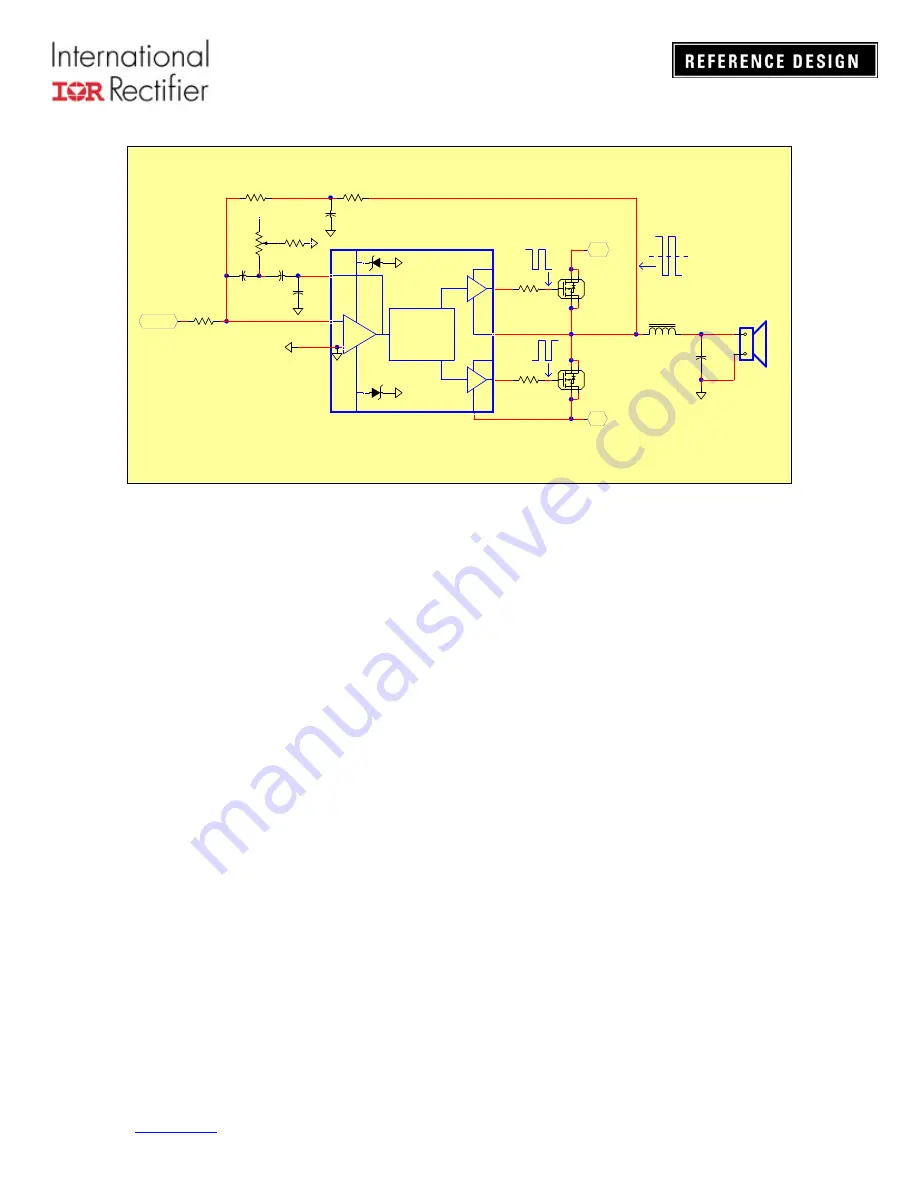

R13

IN-

C23

R21

COMP

.

R33

IRS2092S

LO

COM

VS

VCC

VB

-B

+B

LP Filter

0V

C1

HO

INPUT

CH1

C21

P1

R31

Integrator

Modulator

and

Shift level

GND

C17

IRF6645

Q4

IRF6645

Q3

Self Oscillating determined components

Fig 30

Adjustments of Self-Oscillating Frequency

The PWM switching frequency in this type of self-oscillating switching scheme greatly impacts

the audio performance, both in absolute frequency and frequency relative to the other channels. In

absolute terms, at higher frequencies distortion due to switching-time becomes significant, while

at lower frequencies, the bandwidth of the amplifier suffers. In relative terms, interference

between channels is most significant if the relative frequency difference is within the audible

range. Normally, when adjusting the self-oscillating frequency of the different channels, it is best

to either match the frequencies accurately, or have them separated by at least 25kHz. With the

installed components, it is possible to change the self-oscillating frequency from about 300kHz

up to 450kHz, as shown on Fig 30

Switches and Indicators

There are four different indicators on the reference design as shown in the figure 31 below:

1.

An orange LED, signifying a fault / shutdown condition when lit.

2.

A green LED on the motherboard, signifying conditions are normal and no fault

condition is present.

3.

A blue LED on the daughter board module, signifying there are HO pulses for CH1

4.

A blue LED on the daughter board module signifying there are HO pulses for CH2

There are three switches on the reference design:

1.

Switch S1 is a trip and reset push-button. Pushing this button has the same effect as a

fault condition. The circuit will restart about three seconds after the shutdown button is

released.

2.

Switch S2 is an internal clock-sync frequency selector. This feature allows the designer

to modify the switching frequency in order to avoid AM radio interference. With S3 set

to INT, the two settings “H” and “L” will modify the internal clock frequency by about

Summary of Contents for IRAUDAMP5

Page 45: ...www irf com Pa Figure 39 PCB Layout Motherboard ge 44 of 50 IRAUDAMP5 REV 3 1 Top Layer ...

Page 46: ...www irf com Top silk screen Page 45 of 50 IRAUDAMP5 REV 3 1 ...

Page 47: ...www irf com Page 46 of 50 IRAUDAMP5 REV 3 1 Bottom ...

Page 48: ...www irf com Page 47 of 50 IRAUDAMP5 REV 3 1 4 0 ...

Page 49: ...www irf com Page 48 of 50 IRAUDAMP5 REV 3 1 Bottom Silkscreen 4 0 ...