REL 1.2

Page 31 of 82

i.MX6 Qseven PMIC SOM Hardware User Guide

iWave Systems Technologies Pvt. Ltd.

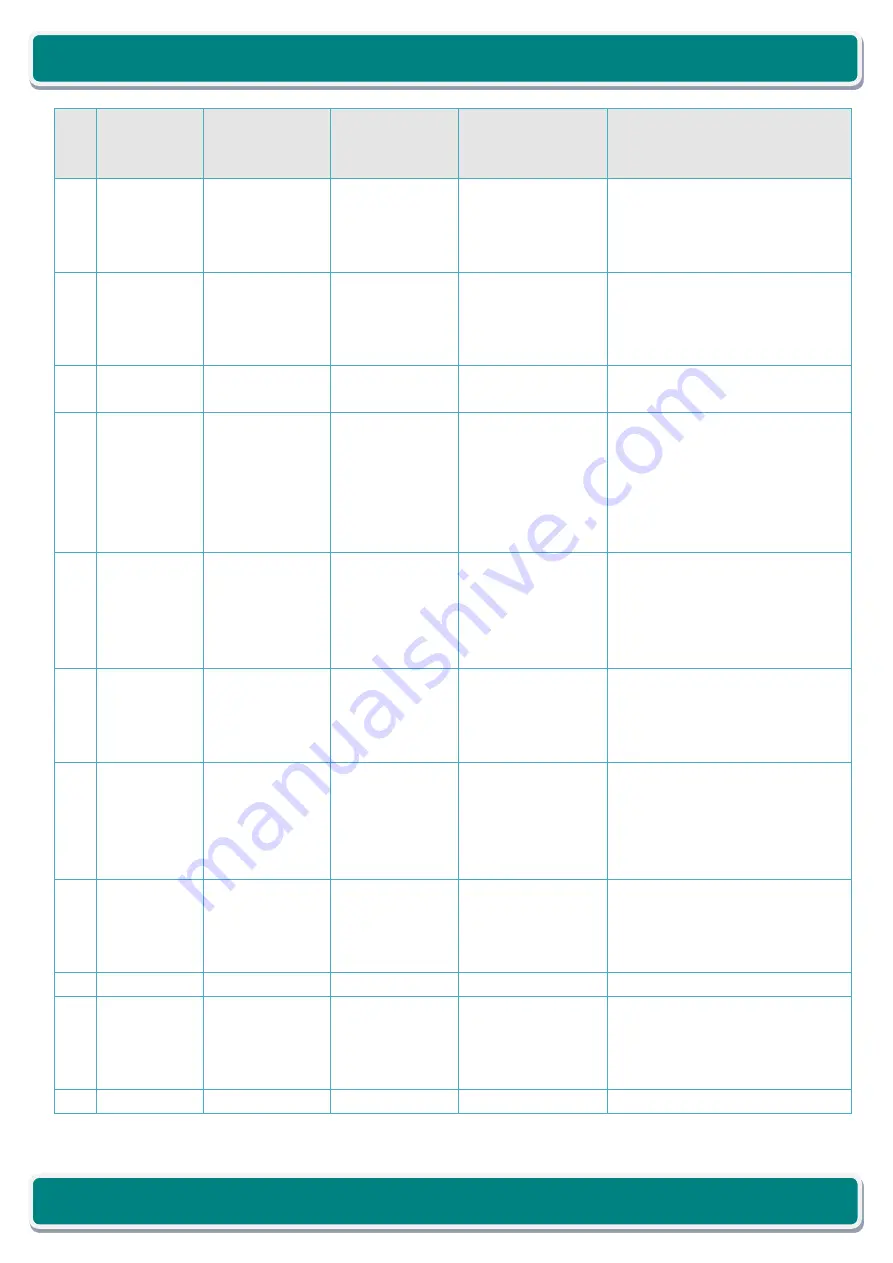

Pin

No.

Qseven Edge

Connector

Pin Name

Signal Name

i.MX6 Ball

Name/

Pin Number

Signal Type/

Termination

Description

61

HDA_RST#/

I2S_RST#

GPIO1_11_HDA

_RST(SD2_CMD)

SD2_CMD/

F19

O, 3.3V CMOS

Audio codec reset.

Note:

SD2_CMD

signal

is

connected to this pin as GPIO for

implementing Audio codec reset.

62

SMB_DAT/

GP1_I2C_DA

T

I2C2_SDA(KEY_

ROW3)

KEY_ROW3/

T7

IO, 3.3V OD/

4.7K PU

I2C2 data.

Note: Same signal is also

connected

to

Qseven

edge

connector 150

th

pin.

63

HDA_BITCLK/

I2S_CLK

AUD4_TXC(SD2

_DAT3)

SD2_DAT3/

B22

O, 3.3V CMOS

Audio transmit clock.

64

SMB_ALERT# GPIO1_10_SMB

_ALERT(SD2_CL

K)

SD2_CLK/

C21

IO, 3.3V CMOS

System Management Bus alert

input.

Note: SD2_CLK is connected to

this pin as GPIO for implementing

SMB

alert

functionality

if

required.

65

HDA_SDI/

I2S_SDI

AUD4_TXD(SD2

_DAT2)

SD2_DAT2/

A23

I, 3.3V CMOS

Audio receive data.

Note: Make sure to enable

AUDMUX_PDCR4 register’s 12th

bit (TXRXEN) in i.MX6 to make

this pin as receive.

66

GP0_I2C_CLK I2C1_SCL(EIM_D

21)

EIM_D21/

H20

O, 3.3V OD/

4.7K PU

I2C1 clock.

Note: Same signal is also

connected

to

Qseven

edge

connector 127

th

& 128

th

pins.

67

HDA_SDO/

I2S_SDO

AUD4_RXD(SD2

_DAT0)

SD2_DAT0/

A22

O, 3.3V CMOS

Audio Transmit data.

Note: Make sure to enable

AUDMUX_PDCR4 register’s 12th

bit (TXRXEN) in i.MX6 to make

this pin as transmit.

68

GP0_I2C_DA

T

I2C1_SDA(EIM_

D28)

EIM_D28/

G23

IO, 3.3V OD /

4.7K PU

I2C1 data.

Note: Same signal is also

connected

to

Qseven

edge

connector 125

th

& 126

th

pins.

69

THRM#

NC

NA

-

NC.

70

WDTRIG#

GPIO6_8_WDTR

IG(NANDF_ALE)

NANDF_ALE/

A16

I, 3.3V CMOS

Watchdog trigger.

Note: NANDF_ALE is connected to

this pin as GPIO for implementing

Watchdog trigger if required

.

71

THRMTRIP#

NC

NA

-

NC.