REL 1.2

Page 27 of 56

i.MX6 SODIMM SOM Hardware User Guide

iWave Systems Technologies Pvt. Ltd.

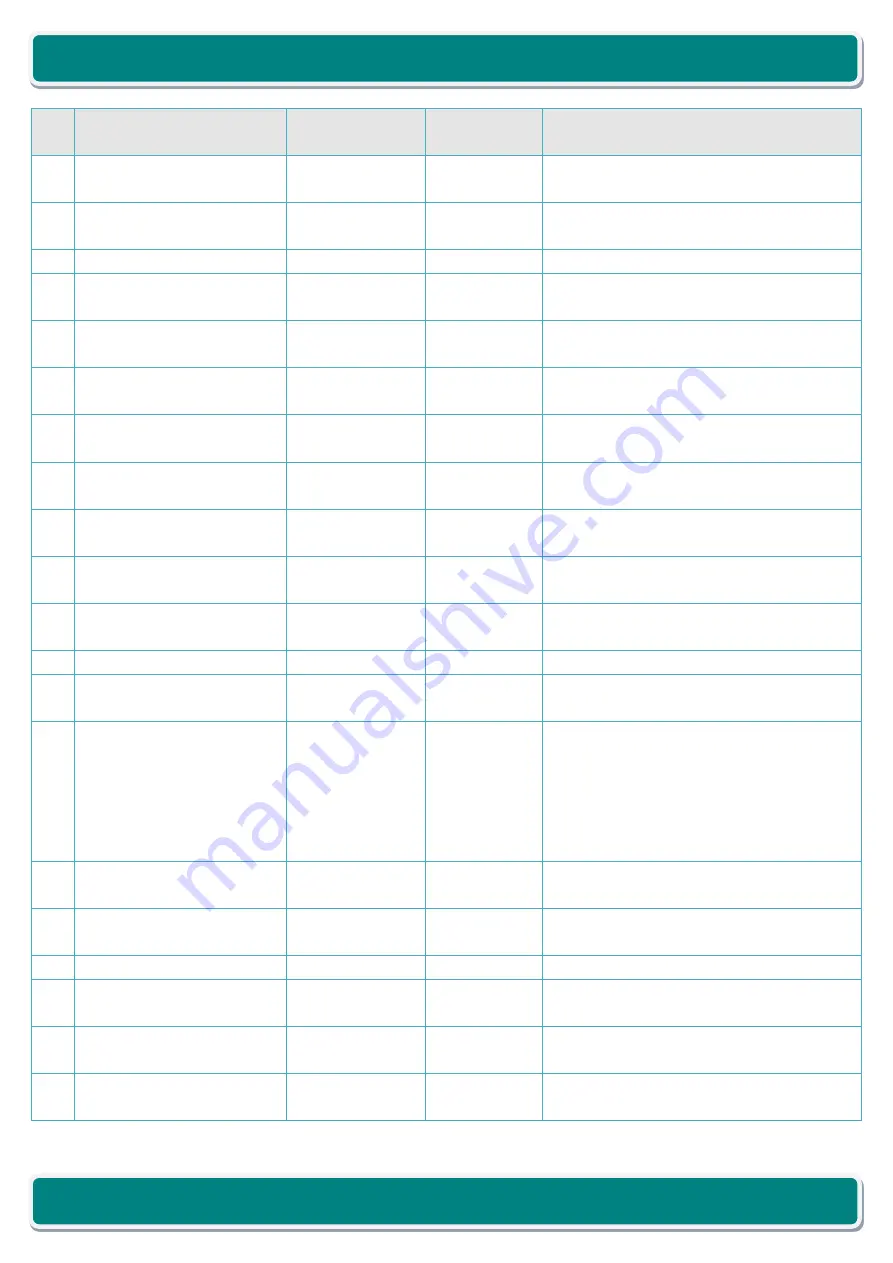

Pin

No.

SODIMM Edge Connector

Pin Name

i.MX6 Ball Name/

Pin Number

Signal Type/

Termination

Description

49

GPIO2_IO01(NANDF_D1)

NANDF_D1/

C17

IO, 3.3V CMOS General Purpose Input/Output.

50

LVDS0_TX0_P

NALVDS0_TX0_P/

U1

O, 2.5V LVDS

LVDS primary channel differential pair 0

positive.

51

GND

NA

Power

Ground.

52

LVDS0_TX1_N

LVDS0_TX1_N/

U4

O, 2.5V LVDS

LVDS primary channel differential pair 1

negative.

53

LVDS0_TX2_N

LVDS0_TX2_N/

V2

O, 2.5V LVDS

LVDS primary channel differential pair 2

negative.

54

LVDS0_TX1_P

LVDS0_TX1_P/

U3

O, 2.5V LVDS

LVDS primary channel differential pair 1

positive.

55

LVDS0_TX2_P

LVDS0_TX2_P/

V1

O, 2.5V LVDS

LVDS primary channel differential pair2

positive.

56

LVDS0_TX3_N

LVDS0_TX3_N/

W2

O, 2.5V LVDS

LVDS primary channel differential pair 3

negative.

57

LVDS0_CLK_N

LVDS0_CLK_N/

V4

O, 2.5V LVDS

LVDS primary channel differential clock

negative.

58

LVDS0_TX3_P

LVDS0_TX3_P/

W1

O, 2.5V LVDS

LVDS primary channel differential pair 3

positive.

59

LVDS0_CLK_P

LVDS0_CLK_P/

V3

O, 2.5V LVDS

LVDS primary channel differential clock

positive.

60

VIN_3V3

NA

I, 3.3V Power

Supply Voltage.

61

AUD4_RXD(SD2_DAT0)

SD2_DAT0/

A22

I, 3.3V CMOS

Audio receive data.

62

eCSPI2_SS1(EIM_LBA)

EIM_LBA/

K22

O, 3.3V CMOS/

10K PD

SPI2 chip select 1.

Important Note: This signal is also used for

i.MX6 CPU bootstrap setting on SOM and so

no external loads or pull-up/pull-down

resistors to be connected to this pin which

will change the boot configuration.

63

eCSPI2_MISO(CSI0_DAT10)

CSI0_DAT10/

M1

I, 3.3V CMOS

SPI2 Master Input Slave Output.

64

CCM_CLKO1(GPIO_19)

GPIO_19/

P5

O, 3.3V CMOS

Observability clock 1 output.

65

GND

NA

Power

Ground.

66

eCSPI2_SCLK(CSI0_DAT8)

CSI0_DAT8/

N6

O, 3.3V CMOS

SPI2 clock signal.

67

AUD4_TXD(SD2_DAT2)

SD2_DAT2/

A23

O, 3.3V CMOS

Audio Transmit data.

68

GPIO6_IO10(NANDF_RB0)

NANDF_RB0/

B16

IO, 3.3V CMOS General Purpose Input/Output.