REL 1.2

Page 49 of 56

iWave Systems Technologies Pvt. Ltd.

i.MX6 SODIMM SOM Hardware User Guide

3.1.3

Power Consumption

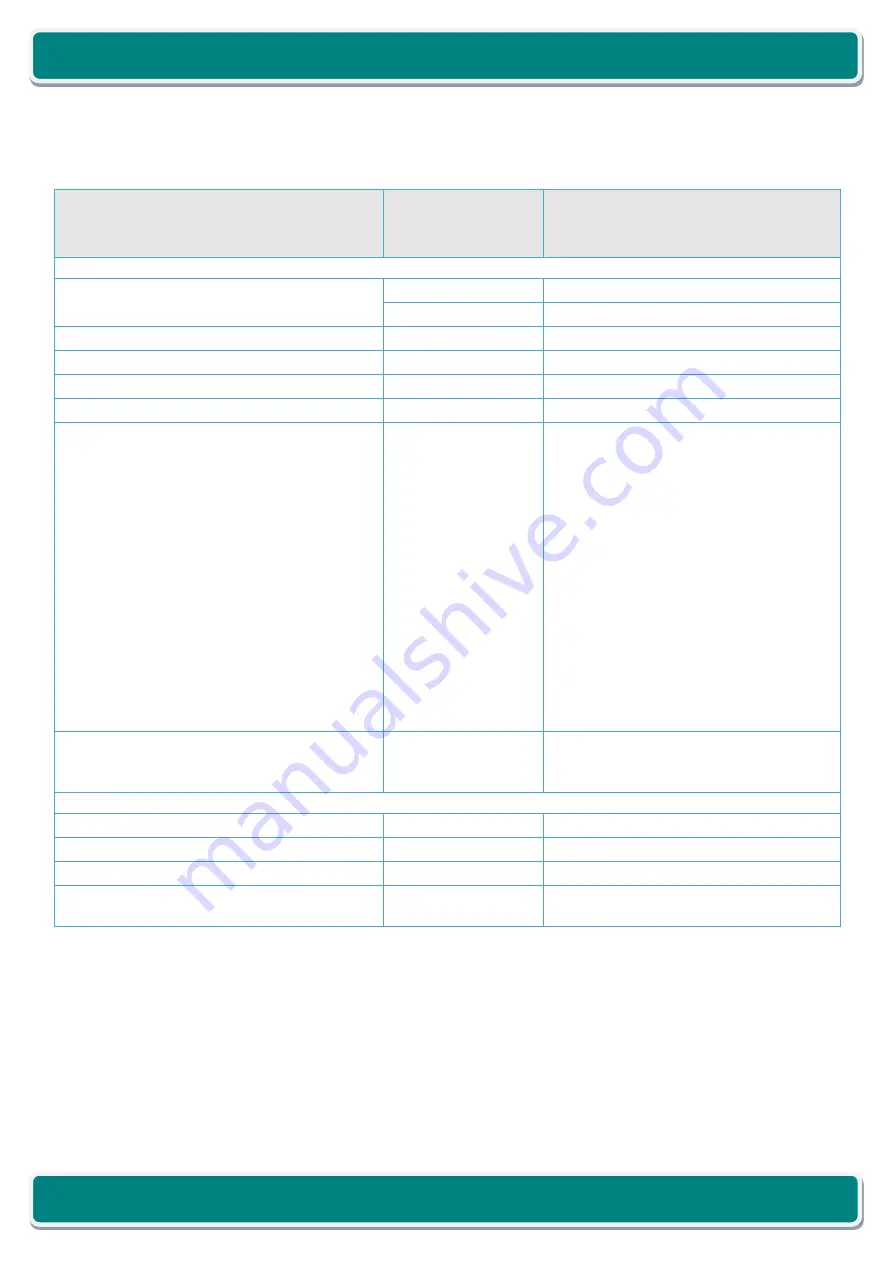

Table 9: Power Consumption

Task/Status

Power Rail

Current Drawn (A)/

Power Consumption (W)

Run Mode Power Consumption¹

Play Video

VIN_3V3

0.49/1.617

VIN_3V3

0.33/1.089

Play Graphics 3D Demo

VIN_3V3

0.46/1.518

Play Audio

VIN_3V3

0.27/0.891

File Transfer

VIN_3V3

0.39/1.287

Dhrystone

VIN_3V3

1.02/3.366

Maximum Power Test:

HDMI - Run the 1080p video

(creature.mp4)

LVDS - Run the video (akiyo.mp4) on

LVDS

Ethernet - Run the ping test

FileTransfer - Transfer the 1MB file

between USB and Micro SD with 1000

count

Audio - Run the mp3 file using Gplay

Powermeasurement1.sh - Run the

dry2 application on back ground

Powermeasurement2.sh - Run the

Graphics (OpenGL) application (tiger)

on LVDS

VIN_3V3

1.18/3.894

All above with below mentioned one change,

HDMI - Run the VGA video (akiyo.mp4) on

HDMI using VPU Decoder library

VIN_3V3

1.09/3.597

Low Power Mode Power Consumption²

System Idle Mode.

VIN_3V3

0.2/0.66

Deep Sleep Mode.

VIN_3V3

0.05/0.165

User Idle Mode - Enable the Bus frequency

VIN_3V3

0.3/0.99

RTC power when no VIN_3V3 supply is

provided

VRTC_3V0

500uA

³

¹ Power consumption measurements have been done in iWave’s i.MX

6 Quad CPU based SODIMM SOM

with iWave’s

Generic SODIMM Carri

er board running iWave’s

Linux3.14.38 BSP (iW-PREPZ-DF-01-R2.0-REL1.0-Linux3.14.38).

² Only i.MX6 CPU related power management is implemented in the BSP for low power modes.

³ i.MX6 RTC controller draws more power from VCC_RTC coin cell power input and so could drain the coin cell faster.