REL1.1

Page 40 of 51

RZ/G1C SBC Hardware User Guide

iWave Systems Technologies Pvt. Ltd.

2.12

RZ/G1C Pin Multiplexing on Expansion Connectors

The RZ/G1C CPU IO pins have many alternate functions and can be configured to any one of the alternate functions based on the requirement. Also most of

the RZ/G1C

CPU’s IO pins can be configured as GPIO if required.

The below table provides the details of RZ/G1C CPU pin connections to the Expansion

connectors with selected pin function highlighted and available alternate functions. This table has been prepared by referring Renesas

’s

RZ/G1C Hardware

User’s Manual

.

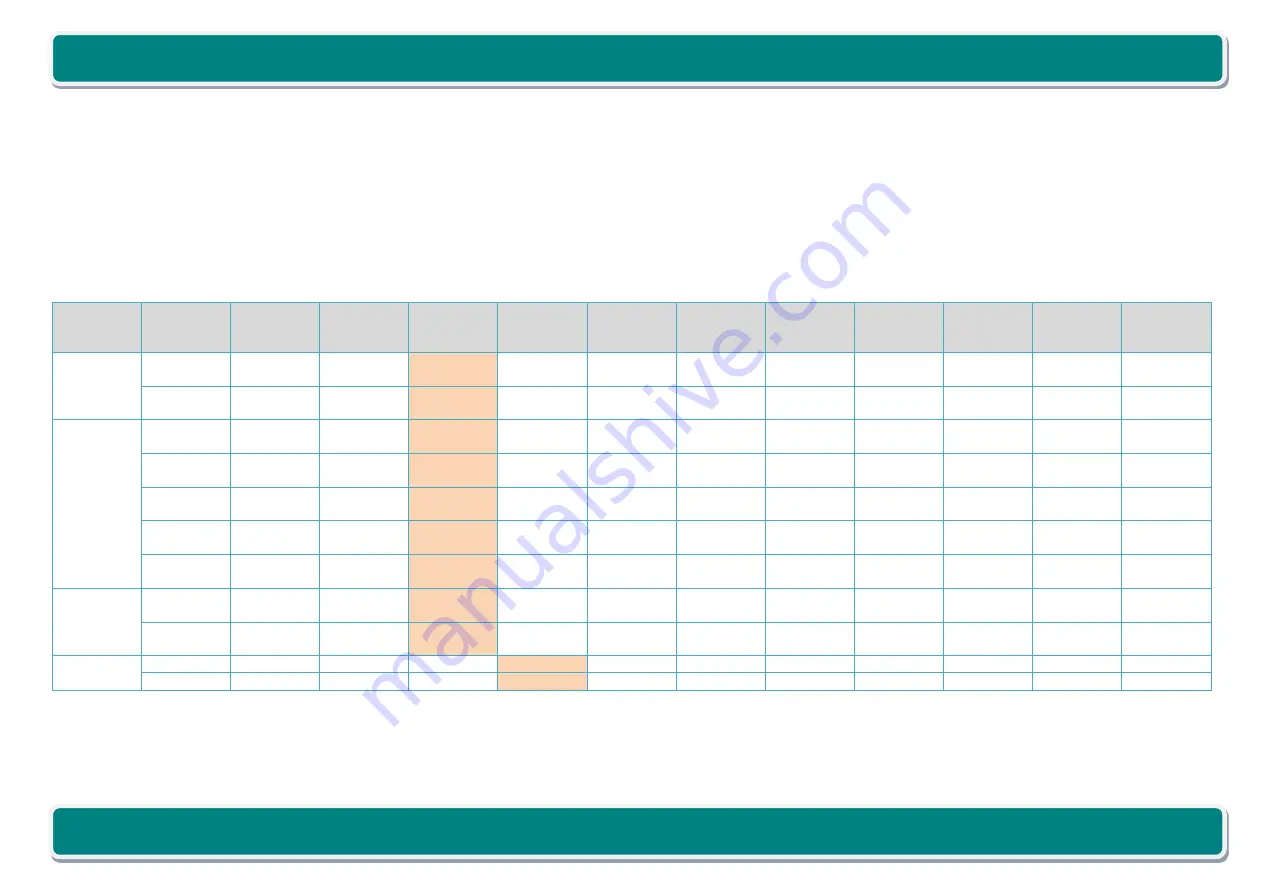

Table 10: RZ/G1C CPU IOMUX for Expansion Connector1 Interfaces

Interface/

Function

Expansion

Connnector1

Pin Numbers

RZ/G1C CPU

Pin Number

Function 1

Function 2

Function 3

Function 4

Function 5

Function 6

Function 7

Function 8

GPIO

Default

State

SCIF2

8

K2

SSI_WS9_A

TX2_B

SDA3_E

VI0_DATA6_

VI0_B6

GP5_26

GP5_26

10

K3

SSI_SCK9_A

RX2_B

SCL3_E

EX_WAIT1

VI0_DATA5_

VI0_B5

GP5_25

GP5_25

MSIOF2

19

Y5

D11

MSIOF2_TXD

_A

HTX0_B

GP1_11

GP1_11

21

AA1

D10

MSIOF2_RXD

_A

HRX0_B

GP1_10

GP1_10

23

Y4

D12

MSIOF2_SCK

_A

HSCK0

CAN_CLK_C

GP1_12

GP1_12

24

Y3

D13

MSIOF2_SYN

C_A

RX4_C

GP1_13

GP1_13

26

Y2

D14

MSIOF2_SS1

TX4_C

CAN1_RX_B

AVB_AVTP_C

APTURE_A

GP1_14

GP1_14

I2C1

27

A4

TX3_A

SDA1_C

MSIOF1_TXD

_B

DU1_DB5

AUDIO_CLKB

_C

SSI_WS4_B

GP4_23

GP4_23

28

B3

RX3_A

SCL1_C

MSIOF1_RXD

_B

DU1_DB4

AUDIO_CLKA

_C

SSI_SDATA4_

B

GP4_22

GP4_22

I2C4

3

D3

SSI_SCK78_A

SDA4_E

DU1_DISP

GP5_6

GP5_6

5

D2

SSI_WS78_A

SCL4_E

DU1_CDE

GP5_7

GP5_7