REL1.1

Page 44 of 51

RZ/G1C SBC Hardware User Guide

iWave Systems Technologies Pvt. Ltd.

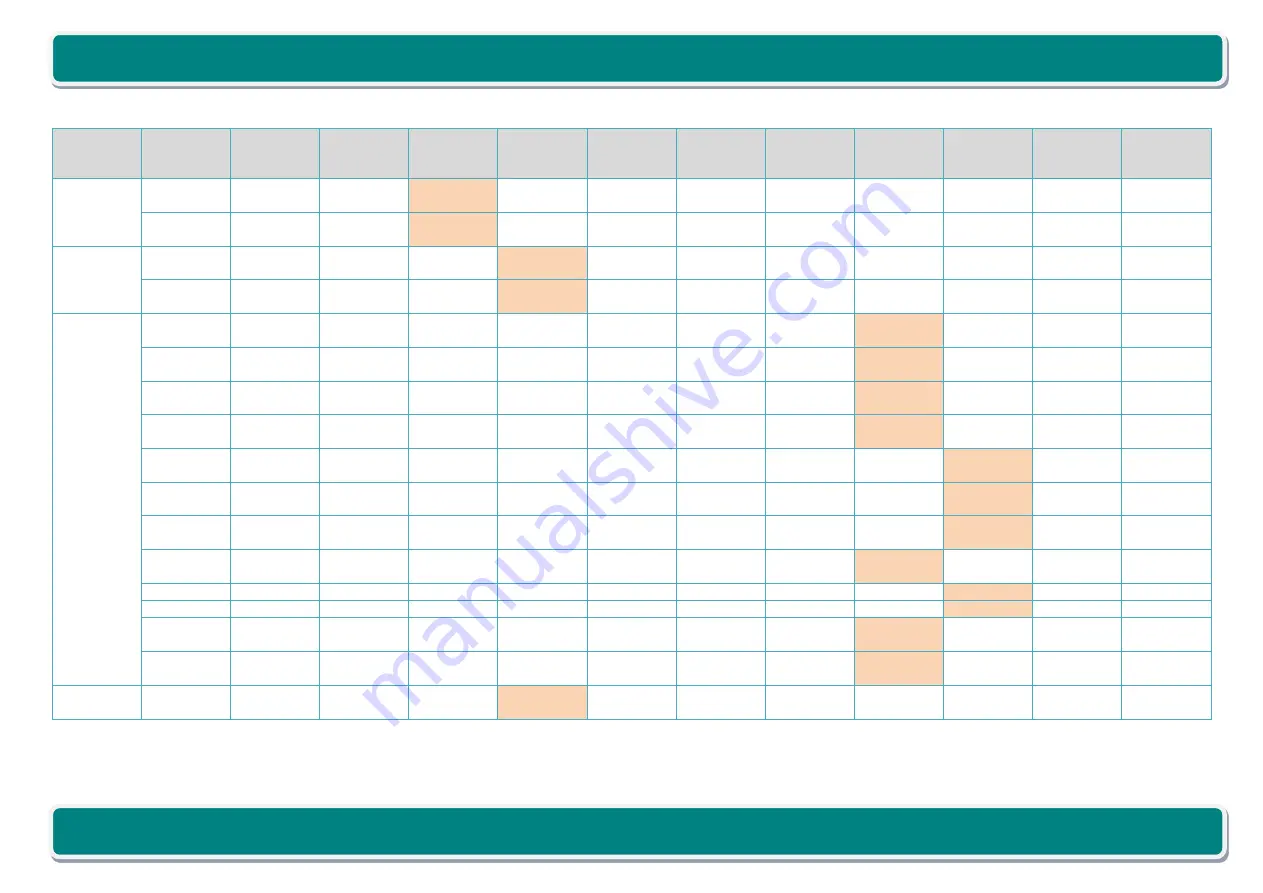

Table 12: RZ/G1C CPU IOMUX for Expansion Connector3 Interfaces

Interface/

Function

Expansion

Connnector3

Pin Numbers

RZ/G1C CPU

Pin Number

Function 1

Function 2

Function 3

Function 4

Function 5

Function 6

Function 7

Function 8

GPIO

Default

State

SCIF1

17

F4

SSI_SDATA8_

A

RX1_B

CAN0_RX_D

AVB_AVTP_C

APTURE_B

VI0_R7

GP5_19

GP5_19

19

H1

SSI_WS1_A

TX1_B

CAN0_TX_D

AVB_AVTP_

MATCH_B

VI0_DATA0_

VI0_B0

GP5_20

GP5_20

SCIF4

18

AC2

D2

Reserved

RX4_B

SCL0_D

PWM1_C

MSIOF2_SCK

_C

SSI_SCK5_B

GP1_2

GP1_2

20

AC1

D3

Reserved

TX4_B

SDA0_D

PWM0_A

MSIOF2_SYN

C_C

GP1_3

GP1_3

VI0

1

H2

SSI_SCK1_A

SCIF1_SCK_B

PWM1_D

IRQ9

REMOCON_

A

DACK2

VI0_CLK

AVB_COL

GP5_18

GP5_18

2

E4

AUDIO_CLKC

_A

SCL4_B

Reserved

VI0_HSYNC#

GP5_30

GP5_30

3

E1

AUDIO_CLKO

UT_A

SDA4_B

Reserved

VI0_VSYNC#

GP5_31

GP5_31

4

E2

AUDIO_CLKA

_A

SCL0_B

Reserved

TANS1

VI0_CLKENB

GP5_28

GP5_28

8

A6

MSIOF0_RXD

_A

RX5_A

SCL2_C

DU1_DR2

QSPI1_MOSI

/QSPI1_IO0

SSI_SDATA6_

B

VI0_G2

GP4_4

GP4_4

9

A5

MSIOF0_SCK

_A

IRQ0

Reserved

DU1_DR4

Reserved

QSPI1_SPCLK

SSI_SCK78_B

VI0_G4

GP4_6

GP4_6

10

B6

MSIOF0_TXD

_A

TX5_A

SDA2_C

DU1_DR3

QSPI1_MISO

/QSPI1_IO1

SSI_WS78_B

VI0_G3

GP4_5

GP4_5

11

G1

SSI_WS0129

_A

MSIOF1_TXD

_A

TX5_D

VI0_G7

GP5_10

GP5_10

12

C5

SCL1_A

RX4_A

PWM5_D

DU1_DR0

SSI_SCK6_B

VI0_G0

GP4_2

GP4_2

13

D5

SDA1_A

TX4_A

DU1_DR1

SSI_WS6_B

VI0_G1

GP4_3

GP4_3

14

F5

SSI_SDATA7_

A

IRQ8

AUDIO_CLKA

_D

CAN_CLK_D

VI0_G5

GP5_8

GP5_8

16

G2

SSI_SCK0129

_A

MSIOF1_RXD

_A

RX5_D

VI0_G6

GP5_9

GP5_9

PWM2

7

K1

SSI_SDATA9_

A

SCIF2_SCK_B

PWM2_D

VI0_DATA7_

VI0_B7

GP5_27

GP5_27