REL0.1

Page 24 of 95

Kintex Ult FPGA SOM Hardware User Guide

iWave Systems Technologies Pvt. Ltd.

* Signal directions mentioned in table are based on LS1021A chip.

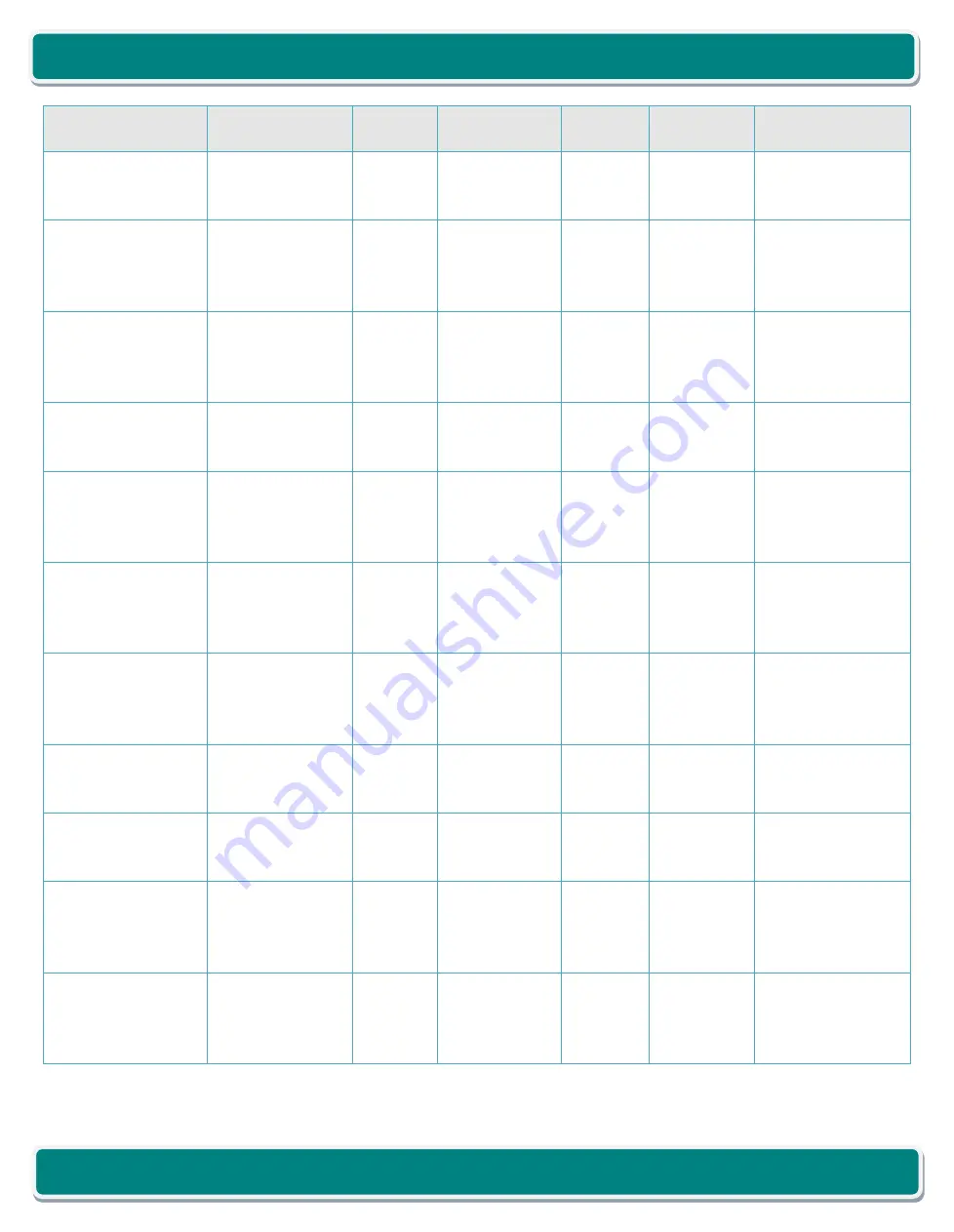

Signal Name

LS1021A Pin Name

LS1021A

Pin No

KU19P Pin

Name

KU19P Pin

No.

Signal Type/

Termination

*

Description

LS_EC3_TXD1_PL_BF2

5_L5N_65

EC3_TXD1/GPIO3_

30/TSEC_1588_CLK

_OUT/FTM3_CH5

W3

IO_L5N_T0U_N

9_AD14N_A23_

65

BF25

O, 1.8V

Transmit Data

LS_EC3_TXD2_PL_BE2

5_L5P_65

EC3_TXD2/GPIO3_

29/TSEC_1588_ALA

RM_OUT1/FTM3_C

H6

V4

IO_L5P_T0U_N8

_AD14P_A22_6

5

BE25

O, 1.8V

Transmit Data

LS_EC3_TXD3_PL_BE2

6_L4N_65

EC3_TXD3/GPIO3_

28/TSEC_1588_ALA

RM_OUT2/FTM3_C

H7

V3

IO_L4N_T0U_N

7_DBC_AD7N_A

25_65

BE26

O, 1.8V

Transmit Data

LS_EC3_TXEN_PL_BD2

6_L4P_65

EC3_TX_EN/GPIO4

_00/EC1_TX_ER/FT

M3_CH1

Y3

IO_L4P_T0U_N6

_DBC_AD7P_A2

4_65

BD26

O, 1.8V

Transmit Enable

LS_EC3_RXCLK_PL_BE

28_L3N_65

EC3_RX_CLK/GPIO4

_07/TSEC_1588_CL

K_IN/FTM3_QD_PH

A

V2

IO_L3N_T0L_N5

_AD15N_A27_6

5

BE28

I, 1.8V

Receive Clock

LS_EC3_RXD0_PL_BD

28_L3P_65

EC3_RXD0/GPIO4_

06/TSEC_1588_TRI

G_IN2/EC2_CRS/FT

M3_CH2

AA1

IO_L3P_T0L_N4

_AD15P_A26_6

5

BD28

I, 1.8V

Receive Data

LS_EC3_RXD1_PL_BF2

7_L2N_65

EC3_RXD1/GPIO4_

05/TSEC_1588_PUL

SE_OUT1/FTM3_C

H3

Y2

IO_L2N_T0L_N3

_FWE_FCS2_B_

65

BF27

I, 1.8V

Receive Data

LS_EC3_RXD2_PL_BE2

7_L2P_65

EC3_RXD2/GPIO4_

04/EC1_COL/FTM3

_EXTCLK

Y1

IO_L2P_T0L_N2

_FOE_B_65

BE27

I, 1.8V

Receive Data

LS_EC3_RXD3_PL_BF2

9_L1N_65

EC3_RXD3/GPIO4_

03/EC1_CRS/FTM3

_FAULT

W1

IO_L1N_T0L_N1

_DBC_RS1_65

BF29

I, 1.8V

Receive Data

LS_EC3_RXDDV_PL_B

F28_L1P_65

EC3_RX_DV/GPIO4

_08/TSEC_1588_TR

IG_IN1/FTM3_QD_

PHB

AA2

IO_L1P_T0L_N0

_DBC_RS0_65

BF28

I, 1.8V

Receive Data Valid

LS_EC3_GTXCLK125_P

L_AM27_L23P_65

EC3_GTX_CLK125/

GPIO4_02/EC2_CO

L/USB2_DRVVBUS/

EC3_RX_ER

Y4

IO_L23P_T3U_N

8_I2C_SCLK_65

AM27

I, 1.8V

RGMII TX Reference

Clock