REL0.1

Page 66 of 95

Kintex Ult FPGA SOM Hardware User Guide

iWave Systems Technologies Pvt. Ltd.

2.9.1

FPGA Interfaces

The interfaces which are supported in Board-to-Board Connector3 from Kintex Ult FPGA

’s PL is explained in the following

section.

2.9.1.1

GTY High Speed Transceivers

The Kintex Ult FPGA (KU19P) supports 20 GTY transceivers through Four transceiver Quad (Bank 228, 229, 230, 231 & 232)

with line rate from 500Mbps to 32.75Gbps based on the speed grade of the FPGA. These transceivers can be used to interface to

multiple high-speed interface protocols. Each GTY transceiver quad supports two dedicated reference clock input pairs.

In Kintex Ult FPGA SOM, on board reference clock to the GTY transceiver quad is not supported. This must be fed from the

carrier board based on the peripheral standards used on GTY transceivers. This gives full flexibility to end user to select the required

peripheral standards on GTY transceivers. Also, On board termination and AC coupling capacitor are not supported on transceiver

lines and has to be taken care in the carrier board as recommend.

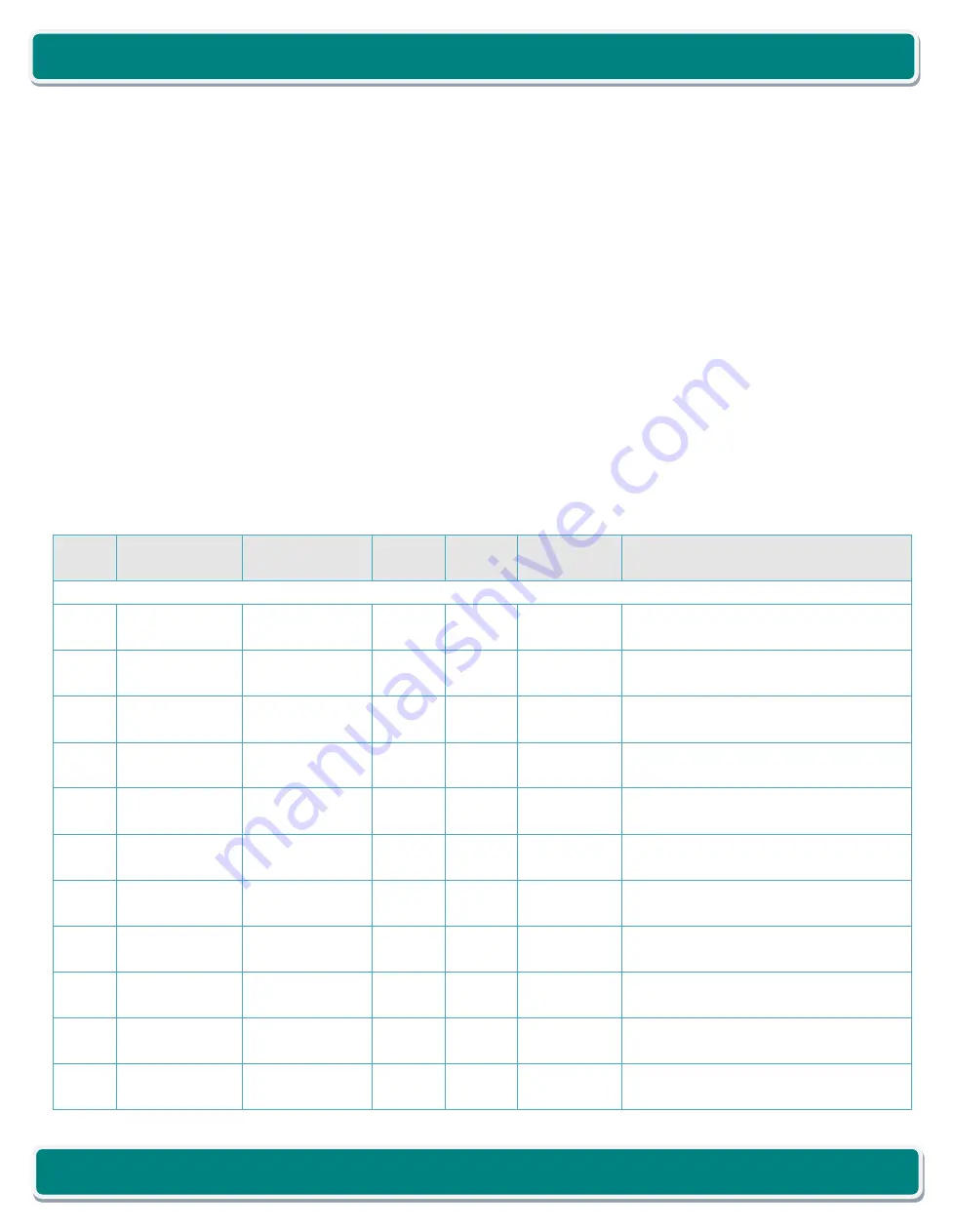

For more details on GTY transceiver pinouts on Board-to-Board Connector3, refer the below table.

B2B-3

Pin No

B2B Connector3

Signal Name

FPGA Pin Name

FPGA

Bank

FPGA

Pin No

Signal Type/

Termination

Description

Bank228 Transceiver Quad Pins

D2

B2B_GTREFCLK0

P_228*

MGTREFCLK0P_2

28

228

AH11

I, DIFF

GTY Bank228 channel0 High speed

differential reference clock0 positive.

D3

B2B_GTREFCLK0

N_228*

MGTREFCLK0N_

228

228

AH10

I, DIFF

GTY Bank228 channel0 High speed

differential reference clock0 negative.

D6

B2B_GTYRXP3_2

28*

MGTYRXP3_228

228

AF2

I, DIFF

GTY Bank228 channel3 High speed

differential receiver positive.

D7

B2B_GTYRXN3_

228*

MGTYRXN3_228

228

AF1

I, DIFF

GTY Bank228 channel3 High speed

differential receiver negative.

D10

GTYRXP2_228

MGTYRXP2_228

228

AG4

I, DIFF

GTY Bank228 channel2 High speed

differential receiver positive.

D11

GTYRXN2_228

MGTYRXN2_228

228

AG3

I, DIFF

GTY Bank228 channel2 High speed

differential receiver negative.

D14

GTYRXP1_228

MGTYRXP1_228

228

AH2

I, DIFF

GTY Bank228 channel1 High speed

differential receiver positive.

D15

GTYRXN1_228

MGTYRXN1_228

228

AH1

I, DIFF

GTY Bank228 channel1 High speed

differential receiver negative.

D18

GTYRXP0_228

MGTYRXP0_228

228

AJ4

I, DIFF

GTY Bank228 channel0 High speed

differential receiver positive.

D19

GTYRXN0_228

MGTYRXN0_228

228

AJ3

I, DIFF

GTY Bank228 channel0 High speed

differential receiver negative.

D22

B2B_GTYTXN3_

228*

MGTYTXN3_228

228

AF6

O, DIFF

GTY Bank228 channel3 High speed

differential transmitter negative.