REL0.1

Page 71 of 95

Kintex Ult FPGA SOM Hardware User Guide

iWave Systems Technologies Pvt. Ltd.

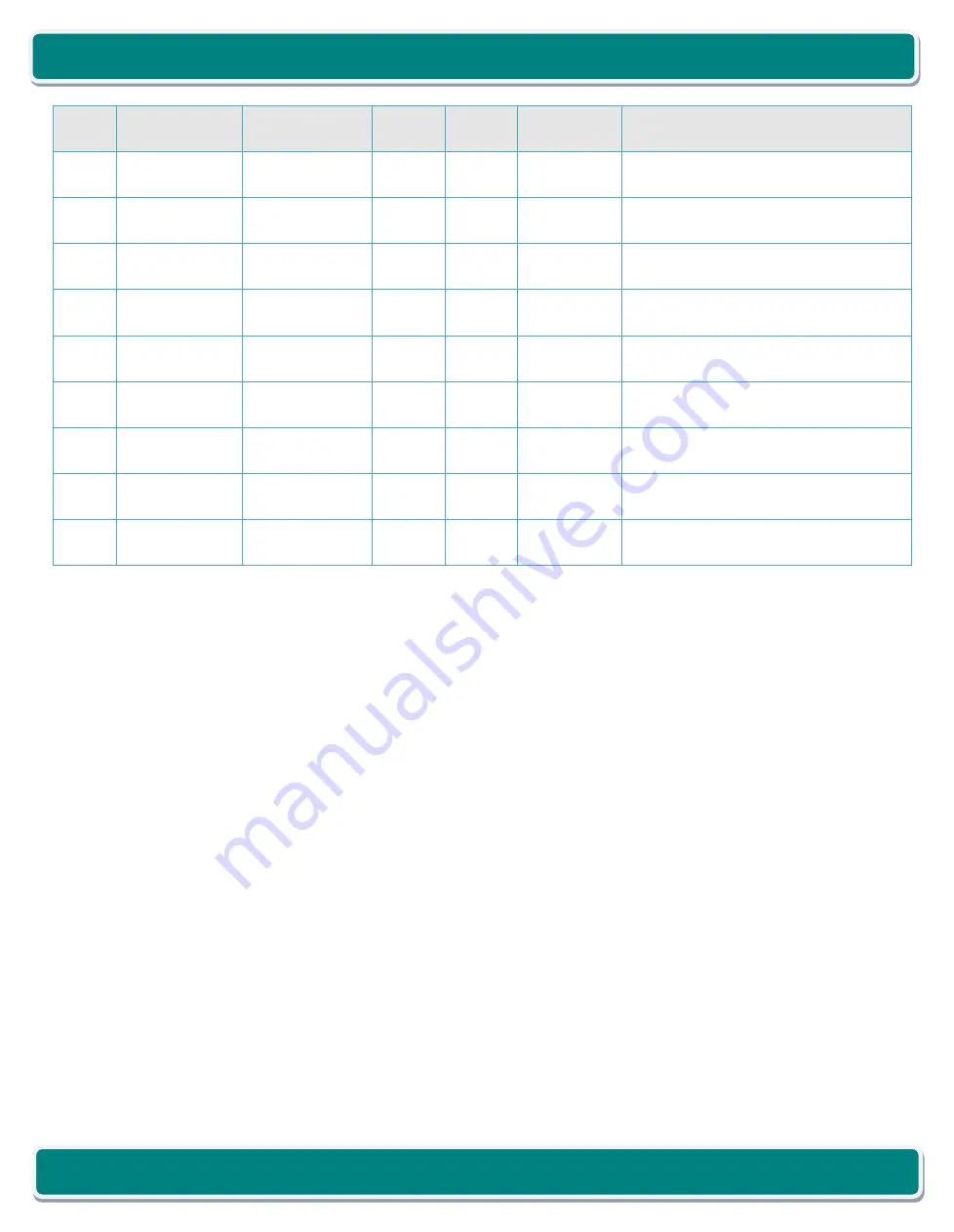

B2B-3

Pin No

B2B Connector3

Signal Name

FPGA Pin Name

FPGA

Bank

FPGA

Pin No

Signal Type/

Termination

Description

D43

GTYRXP1_232

MGTYRXP1_232

232

H2

I, DIFF

GTY Bank232 channel1 High speed

differential receiver positive.

D46

GTYRXN3_232

MGTYRXN3_232

232

F1

I, DIFF

GTY Bank232 channel3 High speed

differential receiver negative.

D47

GTYRXP3_232

MGTYRXP3_232

232

F2

I, DIFF

GTY Bank232 channel3 High speed

differential receiver positive.

D50

GTYRXN0_232

MGTYRXN0_232

232

J3

I, DIFF

GTY Bank232 channel0 High speed

differential receiver negative.

D51

GTYRXP0_232

MGTYRXP0_232

232

J4

I, DIFF

GTY Bank232 channel0 High speed

differential receiver positive.

D54

GTYTXP2_232

MGTYTXP2_232

232

G9

O, DIFF

GTY Bank232 channel2 High speed

differential transmitter positive.

D55

GTYTXN2_232

MGTYTXN2_232

232

G8

O, DIFF

GTY Bank232 channel2 High speed

differential transmitter negative.

D58

GTYTXP3_232

MGTYTXP3_232

232

F7

O, DIFF

GTY Bank232 channel3 High speed

differential transmitter positive.

D59

GTYTXN3_232

MGTYTXN3_232

232

F6

O, DIFF

GTY Bank232 channel3 High speed

differential transmitter negative.

*One GTY transceiver link is connected with on-SOM PCIe transceiver.

2.9.2

Power

The Kintex Ult FPGA SOM works with 5V power input (VCC) from Board-to-Board Connector2 and generates all other

required powers internally On-SOM itself. Also, in Board-to-Board Connector3, Ground pins are distributed throughout the

connector for better performance.

For more details on Power pins on Board-to-Board Connector3, refer the below table.