REL0.1

Page 35 of 95

Kintex Ult FPGA SOM Hardware User Guide

iWave Systems Technologies Pvt. Ltd.

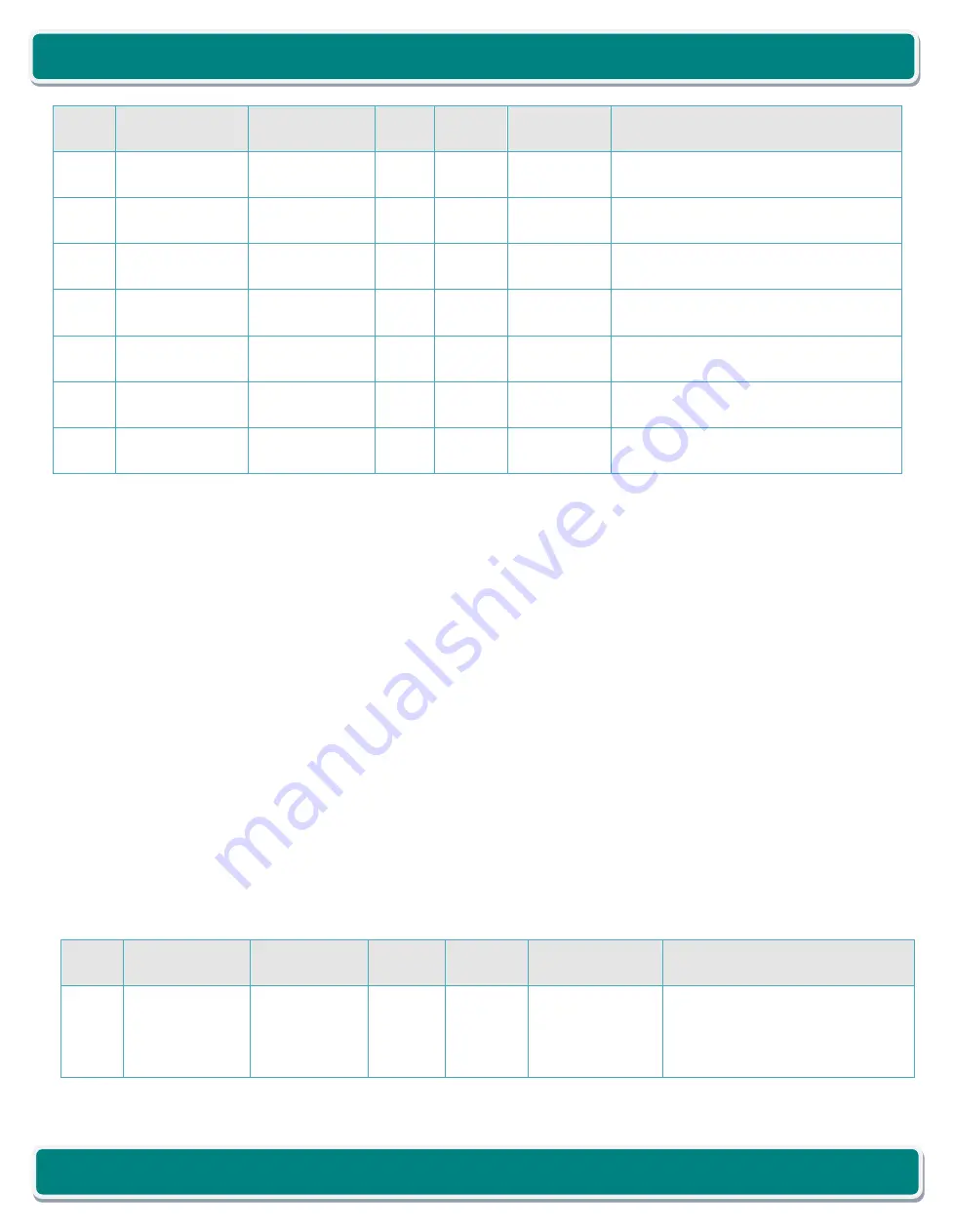

B2B-1

Pin No

B2B Connector1

Signal Name

SoC Pin Name

SoC

Bank

SoC Pin

No

Signal Type/

Termination

Description

137

GTYRXP3_226

MGTYRXP3_226

226

AP2

I, DIFF

GTY Bank226 channel3 High speed

differential receiver positive.

141

GTYRXN2_226

MGTYRXN2_226 226

AR3

I, DIFF

GTY Bank226 channel2 High speed

differential receiver negative.

143

GTYRXP2_226

MGTYRXP2_226

226

AR4

I, DIFF

GTY Bank226 channel2 High speed

differential receiver positive.

98

GTREFCLK0P_226 MGTREFCLK0P_

226

226

AT11

I, DIFF

GTY Bank226 differential reference clock0

positive.

100

GTREFCLK0N_22

6

MGTREFCLK0N_

226

226

AT10

I, DIFF

GTY Bank226 differential reference clock0

negative.

158

GTREFCLK1P_226 MGTREFCLK1P_

226

226

AP11

I, DIFF

GTY Bank226 differential reference clock0

positive.

160

GTREFCLK1N_22

6

MGTREFCLK1N_

226

226

AP10

I, DIFF

GTY Bank226 differential reference clock1

negative.

2.7.2.2

FPGA IOs

–

HD BANK92

The Kintex Ult FPGA SOM supports 11 DIFF IOs/22 Single Ended (SE) IOs on Board-to-Board Connector1 from FPGA High-

Density (HD) Bank92. Upon these 11 DIFF IOs/22 SE IOs, up to 3 HDGC Global Clock Inputs and up to 22 PLSYSMON auxiliary analog

inputs are available.

The IO voltage of Bank92 is connected from LDO1 output of the PMIC and supports variable IO voltage setting. IO voltage is

configurable from 1.2V to 3.3V through software. While using as DIFF IOs or Single Ended IOs, make sure to set the PMIC LDO1 to

output appropriate IO voltage for Bank92. By default, IO voltage of Bank92 is set as 1.2V and after U-boot bootup configurable to

1.8V. For more details about supported IO standard, refer the Kintex Ult FPGA datasheet.

In the Kintex Ult FPGA SOM, Bank92 signals are routed as LVDS IOs to Board-to-Board Connector1. Even though Bank92

signals are routed as DIFF IOs, these pins can be used as SE IOs if required. The Board-to-Board Connector1 pins 22, 24,70, 72, 87,

88, 89, ,90, 91, 93 are HDGC Global Clock Input capable pins of Bank92. Also, Board to Board Connector1 pins 12, 14, 16, 22, 24,

27, 29, 31, 33, 40, 44, 46, 48, 50, 70, 72, 87, 88, 89, 90, 91, 93, and are PLSYSMON auxiliary analog Input capable pins of Bank92.

For more details on HD Bank92 pinouts on Board-to-Board Connector1, refer the below table.

B2B-1

Pin No

B2B Connector1

Signal Name

FPGA Pin

Name

FPGA

Bank

FPGA Pin

No

Signal Type/

Termination*

Description

27

PL_AV24_LVDS9

2_L2P

IO_L2P_AD10P

_92

92

AV24

IO, 3.3V

Bank92 IO2 differential positive.

Same pin can be configured as

SYSMON differential analog input10

positive or Single ended I/O.