ADwin-Pro

Hardware, manual version 2.9, June 2006

111

Pro I: Digital-I/O- and Counter Modules

Pro-CNT-8/32-I Rev. A

ADwin

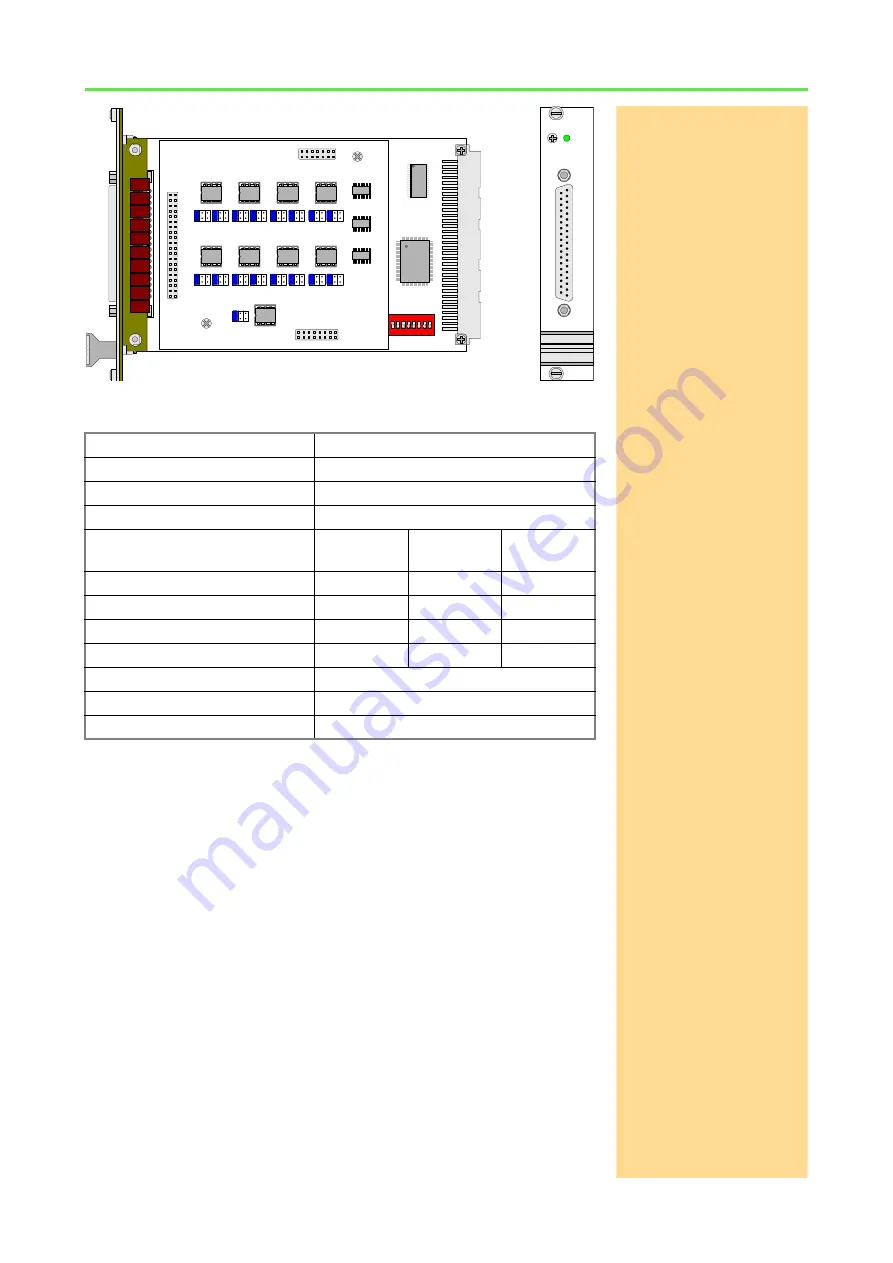

Fig. 209 –

: Board and front panel

Counter

8 up counters

Counter resolution

32 bit

Event input

1

Input current

typ. 7mA / max. 15mA

input voltage range

(selectable via jumpers)

0…5V

0 … 12V

0…24V

Switching threshold for 0-low

0…0.8V

0…1.6V

0…3.2V

Switching threshold for 1-high

4.5…5V

10…12V

20…24V

Input resistance

560

Ω

2 k

Ω

4.3 k

Ω

Input over-voltage

-5V … 8V

-5V … 16V

-5V … 30V

Switching time

200ns

Connector

37-pin DSub socket

Isolation

42V channel-channel / channel-GND

Fig. 210 –

: Specification

19CNT01

ON

1 2 3 4 5 6 7 8

A0 A1 A2 A3 A4 A5 A6 A7

FPGA

FPGA

74A

B

T

16245

74LS19

74LS19

74LS19

74LS19

74LS19

74LS19

74LS19

OCX

FPGA

FPGA

FP

G

A

HCPL-2631

HCPL-2631

HCPL-2631

HCPL-2631

19CNTII1

HCPL-2631

+5

V

+

12V

+

24V

74LS19

HCPL-2631

HCPL-2631

HCPL-2631

HCPL-2631

+5

V

+1

2

V

+2

4

V

+5

V

+1

2

V

+2

4

V

+5

V

+1

2

V

+2

4

V

+5

V

+1

2

V

+2

4

V

+5

V

+1

2

V

+2

4

V

+5

V

+1

2

V

+2

4

V

+5

V

+1

2

V

+2

4

V

+5

V

+1

2

V

+2

4

V

+5

V

+1

2

V

+2

4

V

+5

V

+1

2

V

+2

4

V

+5

V

+1

2

V

+2

4

V

+5

V

+1

2

V

+2

4

V

+5

V

+1

2

V

+2

4

V

+5

V

+1

2

V

+2

4

V

+5

V

+1

2

V

+2

4

V

+5

V

+1

2

V

+2

4

V

74LS19

74LS19

19/37

18/36

17/35

16/34

15/33

14/32

13/31

12/30

11/29

10/28

9/27

8/26

7/25

6/24

5/23

4/22

20/1

Sub-D-

Pin-Nr.:

Sub-D-

Pin-Nr.:

Sub-D-Pin-Nr.:

CNT-8/32-I

COUNTER

INPUT