2 - 16

emPC-CX+

(

System Reference

Manual)

FPGA expansion subsystem

©

Janz Tec AG

Rev. 1.2

2

FPGA expansion subsystem

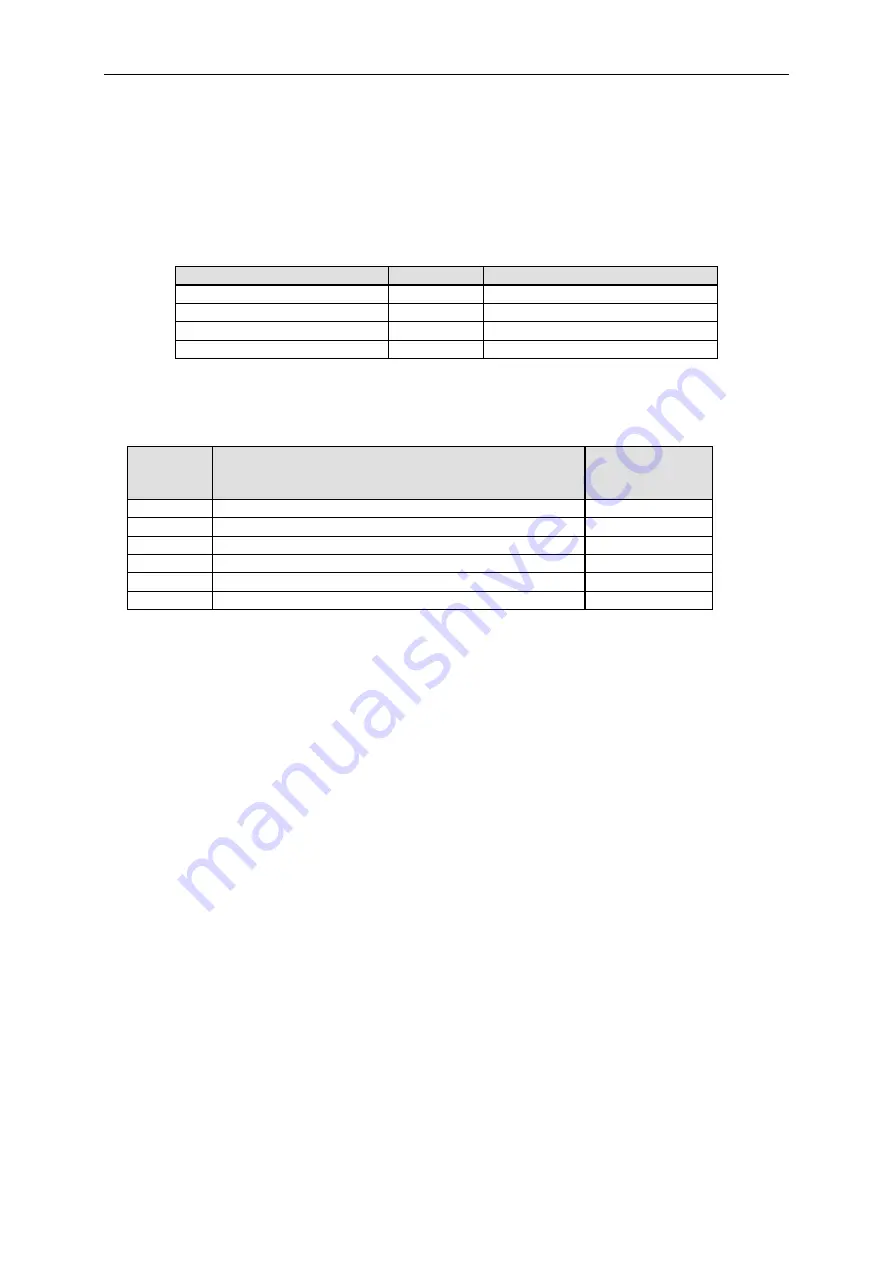

The PCIe interface for special Janz Tec Features is implemented by a FPGA and is identified by a set

of IDs in PCIe configuration space as listed below:

Purpose

Value

Found in

Vendor ID

0x13C3

CFG space register 0x00

Device ID

0x2600

CFG space register 0x02

Subsystem Vendor ID

0x13C3

CFG space register 0x2C

Subsystem ID emPC-CX+

0x2600

CFG space register 0x2E

Table 8: PCI identification

The FPGA PCIe interface provides access to several register spaces.

PCI base

address

register

Description

Size

0

Local configuration registers (memory mapped)

512 B

1

N/A

-

2

CAN/RS232 address space

8 kB

3

Reserved

8 kB

4

Control registers

4 kB

5

NVRAM / IO port address space

1 MB

Table 9: Local address spaces

The actual addresses for these memory spaces are configured by the BIOS of your system every time

the computer is booted. If you wish to access one of these spaces, then you need to read the actual

addresses from the PCIe configuration space.

Summary of Contents for emPC-CX+

Page 8: ......