34

When synchronous DRAM is installed, the number of clock cycles of CAS latency depends

on the DRAM timing. The settings are: 2T and 2.5T.

Note: Change these settings only if you are familiar with the chipset.

SDRAM RAS# to CAS# Delay

This field let’s you insert a timing delay between the CAS and RAS strobe signals, used

when DRAM is written to, read from, or refreshed.

Fast

gives faster performance; and

Slow

gives more stable performance. This field applies only when synchronous DRAM is

installed in the system. The settings are: 2T, 3T and 4T.

SDRAM RAS# Precharge Time

If an insufficient number of cycles is allowed for the RAS to accumulate its charge before

DRAM refresh, the refresh may be incomplete and the DRAM may fail to retain date.

Fast

gives faster performance; and

Slow

gives more stable performance. This field applies only

when synchronous DRAM is installed in the system. The settings are: 2T, 3T and 4T.

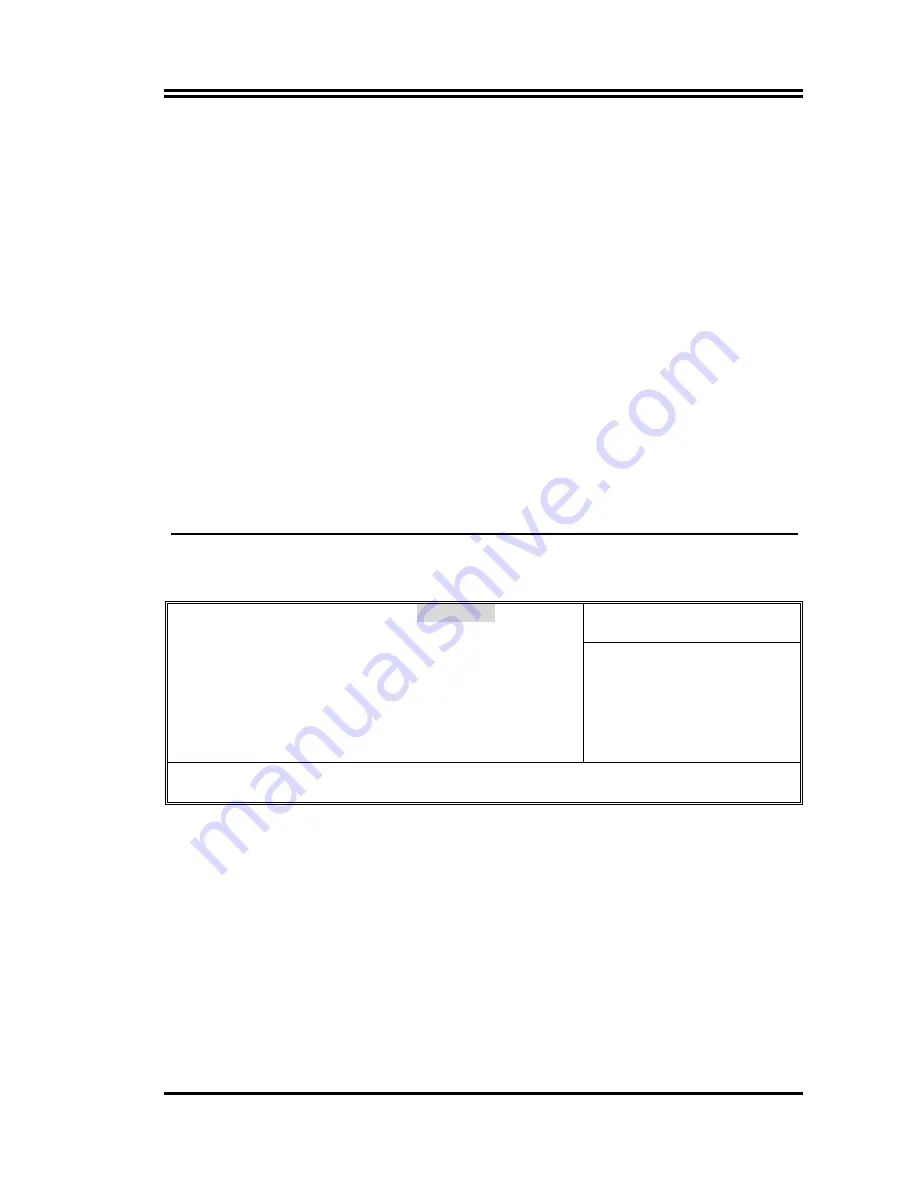

3-8 Integrated Peripherals

CMOS Setup Utility – Copyright(C) 1984-2003 Award Software

Integrated Peripherals

Item Help

> Onboard IDE Function Press Enter

> Onboard Device Function Press Enter

> Onboard Super IO Function Press Enter

Init Display First PCI Slot

Power On Function Button Only

KB Power On Password Enter

Hot Key Power On Ctrl-F1

Power Loss Function Always Off

Menu Level >

↑↓→←

Move Enter:/-/PU/PD:Value F10:Save ESC:Exit F1:General Help

F5:Previous Values F6:Optimized Defaults F7:Standard Defaults

Onboard IDE Function

Please refer to section 3-7-1

Onboard Device Function

Please refer to section 3-7-2

Onboard Super IO Function

Please refer to section 3-7-3

Init Display First

This item allows you to decide to activate whether PCI Slot or AGP VGA first. The

settings are: PCI Slot, AGP Slot.

3-8-1 Onboard IDE Function