A

1

2

3

4

5

B

C

D

E

F

G

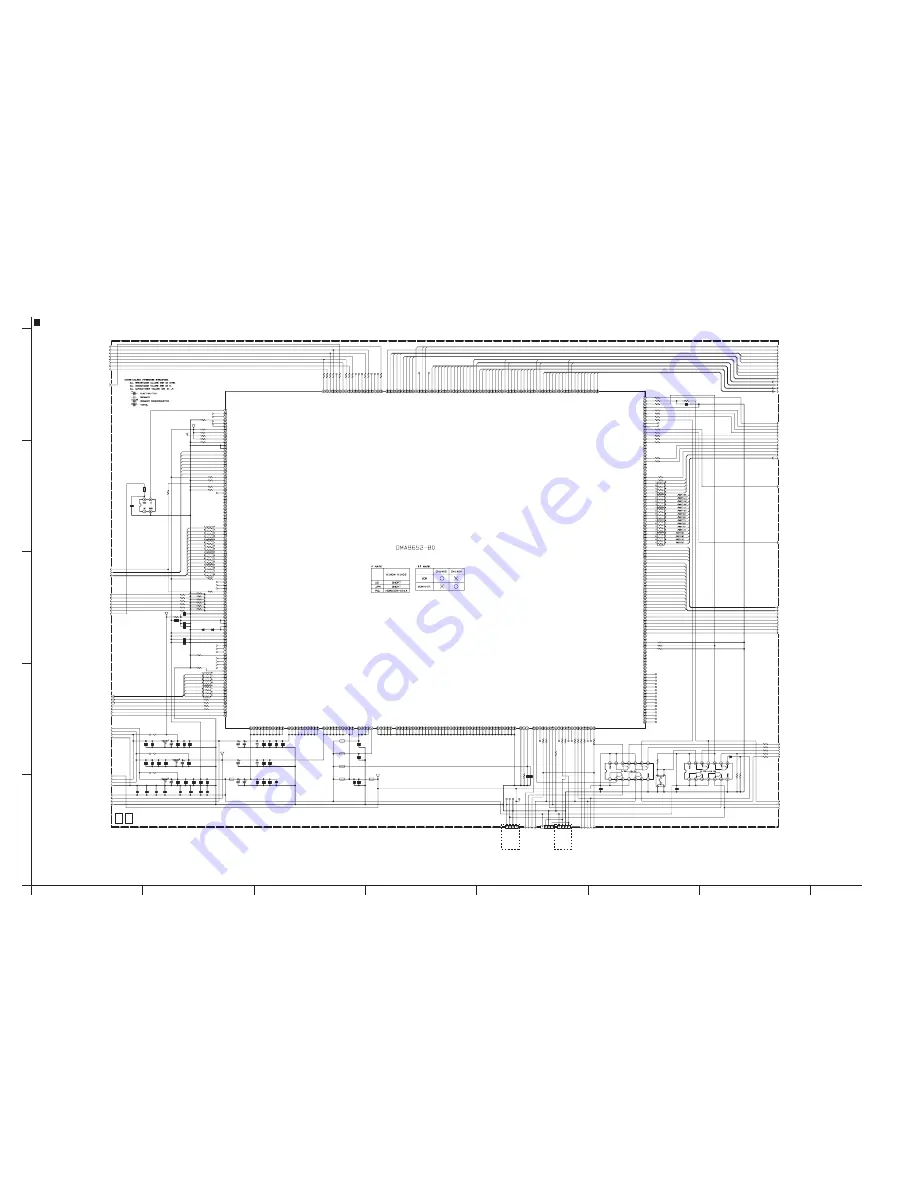

DIGITAL(MEDIA PROCESSOR)

0 2

R1409

PHY_CTL[1]

R1410

R1412

R1413

TL1490

SDRAM_A[0-12]

SDRAM_DQ[0-15]

MADD[22]

SDRAM_DQ[16-31]

SDRAM_VREF

SDRAM_CLK_L[1]

AI_D[0]

R1408

AO_SCLK

AO_FSYNC

R1415

AO_D[0]

TO VIDEO IF

TO 1394PHY

TO VIDEO IF

TO VIDEO IF

TO 1394PHY

TO VIDEO IF

TO VIDEO IF

TO DDR SDRAM

C1403

C1417

R1417

SDRAM_CLK_L[0]

AO_IEC958

AO_MCLKO

R1469

R1411

C1418

C1410

TL1407

C1407

VI_D[2-9]

PHY_DATA[0-7]

PHY_CTL[0]

TL1491

R1459

ATA_DAT[0-15]

WAIT[L]

E5_RESET[L]

TO FLASH

TO VIDEO IF

TO ATAPI IF

TO VIDEO IF

TO 1394PHY

TO FLASH

TO DDR SDRAM

R1472

R1470

C1459

R1461

ATA_ADD[0-4]

VIDEO_27M

C1440

TL1489

SDRAM_DQS[0-3]

RA1401

C1443

ATA_RESET

R1450

RA1411

RA1410

D1403

R1491

TL1449

CS[0]

CS[1]

RA1405

MADD[1-5]

MADD[6-21]

R1462

C1441

R1458

C1449

C1426

C1431

RA1402

RD/WR[L]

R1447

UART2_TX

R1471

ATA_DIOR[L]

ATA_DIOW[L]

VO_D[0-15]

DAC_CVBS_OUT

DAC_SY_OUT

DAC_PR_OUT

C1458

C1457

R1420

ELINK_INT[L]

PHY_RESET[L]

R1465

C1432

RA1403

R1466

R1468

PHY_CLK

PHY_LINK_ON

PHY_LREQ

PHY_LPS

VDDI1.8

DIGI3.3V

R1493

TL1450

C1439

B1403

D2.5V

DAC_PB_OUT

DAC_Y_OUT

R1467

ATA_DMAACK[L]

TL1437

R1453

R1452

DAC_SC_OUT

TL1403

TL1404

R1460

TL1414

R1448

TL1415

C1433

TL1413

TL1417

TL1418

TL1419

TL1420

R1414

V3.3V

ATA_DMARQ

B1402

R1430

R1431

B1401

RA1404

R1429

R1428

ATA_IORDY

LC1401

C1445

ATA_INTRQ

R1416

C1406

TL1451

D1.8V

C1415

C1416

TL1452

C1409

C1402

TL1402

R1498

TL1453

TL1454

C1401

TL1455

C1408

TL1456

K1406

TL1457

UART2_RX

R1497

C1419

K_BUS_OUT

R1446

R1449

DTACK[L]

R1445

TL1458

UWE[L]/UDS[L]

OE[L]/LDS[L]

ALE

D1.8V

LC1402

TL1459

C1411

SDRAM_DQM[0-3]

R1496

TL1460

C1430

C1429

C1428

C1427

VIDEO_MUTE[H]

C1438

C1437

C1436

C1434

C1435

K1402

C1442

TL1461

C1444

C1446

D2.5V

K1405

C1425

C1424

C1423

SDRAM_CLK[1]

SDRAM_CLK[0]

SDRAM_WE_L

SDRAM_CKE

SDRAM_RAS_L

SDRAM_CAS_L

C1412

LC1403

C1405

C1413

C1414

C1422

K1404

K1403

K1401

C1421

GND

K_BUS_REQ

K_BUS_IN

K_BUS_CLK

SYS_RESET[L]

PHY_CNA

C1420

C1404

IC1401

480I[H]

DAC_RST[L]

SDRAM_A[14-17]

R1402

R1419

TL1462

TL1463

TL1464

GND

X1401

C1450

K1407

R1485

R1486

R1487

R1488

R1489

TL1412

R1441

R1421

R1422

R1423

R1424

R1425

R1426

R1427

C1452

GND

C1453

C1454

D1402

D1401

C1455

C1456

K1408

SSTL2_VDD

D3.3V

R1490

RA1406

RA1409

RA1408

RA1407

R1451

TL1485

TL1486

D5.0V

R1474

R1478

R1475

R1479

TL1493

R1476

CN1403

R1480

R1481

R1443

R1473

TL1448

S1401

TL1494

TL1495

IC1404

R1444

IC1405

R1433

R1436

R1432

CN1402

TL1492

C1447

C1448

R1401

R1483

R1438

TL1429

R1477

TL1430

TL1431

R1482

TL1487

TL1432

CN1404

TO JUNCTION

(VIDEO)

CN7105

OPEN

OPEN

R1437

R1440

TL1433

TL1434

R1434

R1435

R1439

A_DAC_CS

TL1488

VIDEO_RXD

VIDEO_CS

TO VIDEO IF

TL1425

TL1423

TL1424

TL1422

TL1436

R1492

VIDEO_RST[L]

TO VIDEO IF

A_MUTE2[H]

SPI_CLK

SPI_MOSI

SPI_CLK

SPI_MOSI

TL1435

OPEN

1SS355

/MDT[0-15]

OPEN

OPEN

OPEN

NQR0415-002X

OPEN

#

OPEN

T

DAC4_OUT

DAC5_OUT

DAC6_OUT

TDI

VO_D[0]/IvGPIOExt[0]

VO_D[3]/IvGPIOExt[3]

VO_D[7]/IvGPIOExt[7]

VO_D[9]/IvGPIOExt[9]

VO_D[13]/IvGPIOExt[13]

VO_D[14]/IvGPIOExt[14]

VO_CLK

VI_CLK[0]

VI_CLK[1]

NQR0415-002X

VO2_D[8]

VI_E[1]/IvGPIOExt[29]

/6.3

VI_VSYNC[0]

VI_D[4]

VI_D[9]

VI_D[7]

/6.3

T

OPEN

T

/6.3

T

SHORT

OPEN

DAC3_OUT

CS[3]

DAC2_OUT

CS[2]

CS[1]

NQR0415-002X

/6.3

CS[0]

ALE

WR[L]/LWE[L]

LDS[L]/OE[L]

MADDR[17]/MDATA[11]

DAC1_OUT

MADDR[19]/MDATA[13]

GPIO[5]

/PCMCIA_IOR[L]

GPIO[4]

/PCMCIA_IOW[L]

MADDR[1]

MADDR[5]

MADDR[24]

CS[5]

#

SHORT

SHORT

ATAPI2_INTRQ

ATAPI2_DMAACK[L]

ATAPI2_ADDR[3]

ATAPI2_DATA[15]

ATAPI2_DATA[14]

ATAPI2_DATA[10]

ATAPI2_DATA[7]

/6.3

T

/6.3

ATAPI2_DATA[4]

ATAPI2_DATA[1]

ATAPI_RESET

ATAPI_ADDR[1]

ATAPI_DMAACK[L]

ATAPI_DATA[1]

ATAPI_DATA[2]

ATAPI_IORDY

ATAPI_ADDR[4]

ATAPI_DATA[9]

CLKX

ATAPI_DATA[8]

1394_LPS

1394_PHY_CLK

1394_PHY_DATA[5]

CLKO_DAC/GPIOExt[35]

HOST_PO_0

DMINUS_1

DMINUS_0

CLKI

ATAPI_DATA[14]

DPLUS_0

DPLUS_1

HOST_OC_0

USB_48MHz/GPIOExt[36]

1394_PHY_DATA[4]

1394_PHY_DATA[7]

1394_LREQ

ATAPI_DATA[7]

ATAPI_DATA[6]

ATAPI_DATA[10]

ATAPI_DATA[3]

ATAPI_DATA[12]

ATAPI_DATA[13]

ATAPI_INTRQ

ATAPI_ADDR[0]

ATAPI2_DATA[3]

ATAPI2_DATA[6]

ATAPI2_DATA[9]

ATAPI2_DATA[13]

ATAPI2_ADDR[0]

ATAPI2_ADDR[4]

ATAPI2_IORDY

CS[4]

MADDR[26]

MADDR[22]

MADDR[2]

GPIO[3]

GPIO[2]

MADDR[15]/MDATA[9]

MADDR[20]/MDATA[14]

MADDR[16]/MDATA[10]

GPIO[1]

MADDR[13]/MDATA[7]

MADDR[7]/MDATA[1]

MADDR[9]/MDATA[3]

RST[L]

VI_D[6]

VI_D[2]

VI_D[3]

VI_D[5]

VI_E[0]

VI_D[1]

VO2_D[6]

VO2_D[3]

VO2_D[0]

VO_E/IvGPIOExt[30]

VO_D[12]/IvGPIOExt[12]

VO_D[8]/IvGPIOExt[8]

VO_D[6]/IvGPIOExt[6]

VO_D[2]/IvGPIOExt[2]

VO_D[1]/IvGPIOExt[1]

VO_HSYNC

TCK

TDO

DAC_DVSS_1

DAC4_OUTB

DAC2_OUTB

USB_AGND_1

USB_AGND_0

1394_PHY_DATA[0]

1394_LINK_ON

HOST_PO_1/GPIOExt[43]

MADDR[18]/MDATA[12]

WAIT[L]

MADDR[3]

MADDR[25]

DAC_VDD_3

DAC_DVDD

TMS

EPD[L]

MCONFIG

ATAPI2_DMARQ

VO2_D[2]

VO2_D[5]

VO2_D[9]

ATAPI2_ADDR[2]

ATAPI2_DATA[11]

ATAPI2_DATA[2]

ATAPI_DATA[15]

UDS[L]/UWE[L]

MADDR[10]/MDATA[4]

ATAPI_DMARQ

ATAPI_ADDR[3]

1394_PHY_DATA[2]

1394_PHY_DATA[1]

1394_PHY_CTL[0]

BYPASS_PLL

HOST_OC_1/GPIOExt[44]

USB_AVDD_1

USB_AVDD_0

DAC_VDD_0

TRST[L]

VO_VSYNC

RSTO[L]

VO_ACTIVE

VO_D[4]/IvGPIOExt[4]

VO_D[5]/IvGPIOExt[5]

VO_D[10]/IvGPIOExt[10]

VO_D[11]/IvGPIOExt[11]

VO_D[15]/IvGPIOExt[15]

VO2_D[1]

VO2_D[4]

VO2_D[7]

VI_D[0]

VI_VSYNC[1]/IvGPIOExt[45]

VI_D[8]

1394_PHY_DATA[6]

MADDR[6]/MDATA[0]

MADDR[11]/MDATA[5]

MADDR[8]/MDATA[2]

MADDR[14]/MDATA[8]

MADDR[12]/MDATA[6]

CS0_8BIT

MADDR[21]/MDATA[15]

1394_PHY_CTL[1]

DTACK[L]

MADDR[4]

GPIO[0]

MADDR[23]

ATAPI2_RESET

ATAPI2_DIOR[L]

ATAPI2_DIOW[L]

ATAPI2_ADDR[1]

ATAPI2_DATA[12]

ATAPI2_DATA[8]

ATAPI2_DATA[5]

ATAPI2_DATA[0]

ATAPI_DIOR[L]

ATAPI_ADDR[2]

ATAPI_DATA[0]

ATAPI_DIOW[L]

1394_PHY_DATA[3]

ATAPI_DATA[5]

ATAPI_DATA[4]

ATAPI_DATA[11]

NAX0580-001X

SHORT

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

SHORT

OPEN

GND

RX

TX

D5.0V

OPEN

SN74HCT08APW

SN74LV08APW

OPEN

OPEN

JRIP_RX

GND

JLIP_TX

D3.3V

##

_1%

OPEN

JRIP_RX

GND

JLIP_TX

D3.3V

##

AO_IEC958

AI_MCLKO

AO_MCLKO

AI_FSYNC

AI_D[0]

AI2_D/GPIO[7]

AO_D[2]

SDRAM_DQ[25]

SDRAM_DQS[3]

SDRAM_DQ[31]

SDRAM_DQ[21]

SDRAM_DQ[18]

SDRAM_DQM[2]

SDRAM_DQM[1]

SDRAM_DQ[14]

SDRAM_DQ[12]

SDRAM_DQ[11]

SDRAM_DQ[9]

SDRAM_DQ[7]

SDRAM_DQ[5]

SDRAM_DQ[3]

SDRAM_WE[L]

SDRAM_A[17]

SDRAM_A[3]

SDRAM_A[6]

SDRAM_A[11]

SDRAM_A[13]

SDRAM_A[9]

SIO_UART1_TX

SIO_UART1_RTS/GPIOExt[41]

SIO_UART2_RX/GPIOExt[37]

SIO_SPI_CS[0]/GPIOExt[24]

SIO_IRTX2

REFVDD

VREF

XTALVDD

XTALVSS

REFVSS

AVDD_2

SIO_IRRX/GPIOExt[39]

SIO_UART1_CTS/GPIOExt[42]

SIO_SPI_CS[1]/GPIOExt[25]

SIO_SPI_MOSI

SIO_UART2_TX/GPIOExt[38]

SIO_UART2_RTS

SDRAM_A[7]

SDRAM_A[5]

SDRAM_A[0]

SDRAM_A[15]

SDRAM_CAS[L]

SDRAM_DQ[2]

SDRAM_DQS[0]

SDRAM_DQ[6]

SDRAM_DQ[8]

SDRAM_DQ[10]

SDRAM_DQS[1]

SDRAM_DQ[13]

SDRAM_DQ[15]

SDRAM_DQ[16]

SDRAM_DQ[19]

SDRAM_DQ[22]

SDRAM_DQ[29]

SDRAM_DQ[26]

AO_D[3]

AO2_D[0]

AO_FSYNC

A2_FSYNC/GPIOExt[34]

AO_MCLKI/GPIOExt[33]

AI_MCLKI/GPIOExt[32]

AVDD_1

AGND_2

AGND_1

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

BIAS_5V01

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

GROUND

VDD_15

GROUND

AVDD_0

VDD_00

VDD_01

VDD_02

VDDP_01

VDDP_02

VDDP_03

VDDP_04

BIAS_5V00

SDRAM_VREF

VDD25_00

A2_SCLK/GPIOExt[31]

VDD_03

AO_D[1]

SDRAM_DQ[24]

SDRAM_DQ[30]

SDRAM_DQM[3]

SDRAM_DQ[20]

VDD25_02

SDRAM_CLK[0]

SDRAM_CLK_L[0]

SDRAM_CLK[1]

SDRAM_CLK_L[1]

VDD_14

VDD25_08

SDRAM_DQ[0]

SDRAM_CKE

SDRAM_A[16]

VDD_30

SDRAM_A[1]

SDRAM_A[8]

SIO_UART2_CTS

VDD_23

SIO_UART1_RX

SIO_SDA

SIO_SPI_CS[2]

VDDP_21

VDDP_20

VDDP_19

VDDP_19A

VDDP_10

VDDP_09

VDDP_08A

VDD_09

VDD_08

AVDD_3

AGND_3

AGND_0

GROUND

VDD25_01

GROUND

AI_SCLK

AI_D[1]/GPIO[6]

AO_SCLK

AO_D[0]

SDRAM_DQ[27]

SDRAM_DQ[28]

SDRAM_DQ[23]

SDRAM_DQS[2]

SDRAM_DQ[17]

VDD25_03

VDD25_04

VDD25_05

VDD25_06

SDRAM_DQM[0]

SDRAM_DQ[4]

SDRAM_DQ[1]

SDRAM_RAS[L]

SDRAM_A[2]

SDRAM_A[4]

SDRAM_A[12]

SDRAM_A[10]

SDRAM_A[14]

SIO_SPI_MISO

SIO_SCL

SIO_SPI_CS[3]

SIO_IRTX1/GPIOExt[40]

SIO_SPI_CLK

OPEN

10k

10k

10k

10k

1k

1k

0.1

0.1

1k

1k

100

0.1

0.1

0.1

100

0‘

1k

100

0.1

100

0.1

100

100

100

1k

100

100

0.1

100

0.1

0.1

0.1

100

100

100

0.1

0.1

100

100

0.1

100

100

100

0

Ω

0.1

100

100

100

100

100

0.1

1k

100

100

100

100

100

0.1

1k

0.1

0.1

0.1

0.1

10k

0.1

0.1

10k

100

100

100

100

10k

0.1

0.1

0.1

10

0.1

0.1

0.1

10

0.1

0.1

0.1

0.1

0.1

0.1

0.1

0.1

100

0.1

0.1

0.1

10

100

0

Ω

100

0.1

10k

100

0.1

0.1

0.1

100

100

100

100

100

100

100

100

100

100

0‘

0‘

4.7k

100

4.7k

100

0.1

0.01

1.18k

100

100

0‘

0‘

100

100

100

100

SDRAM_DQ[0-15]

SDRAM_DQ[16-31]

MADD[22]

CS[0]

VI_D[2-9]

ATA_DAT[0-15]

ATA_DAT[0]

D5.0V

VO_D[0-15]

V3.3V

ATA_DAT[3]

MADD[1-5]

MADD[5]

MADD[4]

MADD[3]

MADD[2]

MADD[1]

ATA_DAT[1]

MADD[21]

ATA_DAT[2]

CS[1]

VI_D[2]

VI_D[3]

VI_D[4]

VI_D[6]

VI_D[5]

MADD[20]

VI_D[7]

MADD[19]

VO_D[0]

VO_D[1]

VO_D[2]

VO_D[3]

VO_D[4]

VO_D[5]

VO_D[6]

VO_D[7]

VO_D[8]

VO_D[9]

VO_D[10]

VO_D[11]

VO_D[12]

VO_D[13]

VO_D[14]

MADD[6-21]

VO_D[15]

MADD[18]

MADD[17]

MADD[16]

MADD[15]

MADD[14]

MADD[13]

MADD[12]

MADD[11]

MADD[10]

MADD[9]

MADD[8]

MADD[7]

MADD[6]

VI_D[8]

PHY_DATA[0-7]

PHY_DATA[7]

PHY_DATA[6]

PHY_DATA[5]

PHY_DATA[4]

PHY_DATA[3]

PHY_DATA[2]

PHY_DATA[1]

PHY_DATA[0]

SDRAM_A[0-12]

SSTL2_VDD

ATA_ADD[0]

ATA_ADD[1]

ATA_ADD[2]

ATA_ADD[3]

ATA_ADD[4]

ATA_DAT[4]

SDRAM_DQM[0-3]

SDRAM_DQS[0-3]

SDRAM_VREF

SDRAM_A[14-17]

ATA_DAT[5]

ATA_DAT[6]

ATA_DAT[7]

ATA_DAT[8]

ATA_DAT[9]

ATA_DAT[10]

ATA_DAT[11]

ATA_DAT[12]

ATA_DAT[13]

ATA_DAT[14]

ATA_DAT[15]

ATA_ADD[0-4]

D3.3V

SDRAM_CAS_L

SDRAM_RAS_L

SDRAM_CKE

SDRAM_WE_L

SDRAM_CLK_L[1]

SDRAM_CLK[1]

SDRAM_CLK_L[0]

SDRAM_CLK[0]

VI_D[9]

VDDI1.8

SDRAM_A[17]

SDRAM_CAS_L

SDRAM_RAS_L

SDRAM_CKE

SDRAM_WE_L

SDRAM_CLK[0]

SDRAM_CLK_L[0]

SDRAM_CLK[1]

SDRAM_A[15]

SDRAM_CLK_L[1]

SDRAM_DQ[0]

SDRAM_A[14]

SDRAM_DQS[3]

SDRAM_DQS[2]

SDRAM_DQ[1]

SDRAM_DQ[2]

SDRAM_DQ[3]

SDRAM_DQ[4]

SDRAM_DQ[5]

SDRAM_DQ[6]

SDRAM_DQ[7]

SDRAM_DQS[1]

SDRAM_DQM[0]

SDRAM_DQ[8]

SDRAM_DQ[9]

SDRAM_DQ[10]

SDRAM_DQ[11]

SDRAM_DQ[12]

SDRAM_DQ[13]

SDRAM_DQ[14]

SDRAM_DQ[15]

SDRAM_DQM[1]

SDRAM_DQS[0]

SDRAM_DQ[16]

SDRAM_DQ[17]

SDRAM_DQ[18]

SDRAM_DQ[19]

SDRAM_DQ[31]

SDRAM_DQ[20]

SDRAM_DQ[21]

SDRAM_DQ[22]

SDRAM_DQM[2]

SDRAM_DQ[23]

SDRAM_DQ[24]

SDRAM_DQ[25]

SDRAM_DQ[26]

SDRAM_DQ[27]

SDRAM_DQ[28]

SDRAM_DQ[29]

SDRAM_DQ[30]

SDRAM_DQM[3]

SDRAM_A[0]

SDRAM_A[1]

SDRAM_A[2]

SDRAM_A[3]

SDRAM_A[4]

SDRAM_A[5]

SDRAM_A[6]

SDRAM_A[7]

SDRAM_A[8]

SDRAM_A[9]

SDRAM_A[10]

SDRAM_A[11]

SDRAM_A[12]

p10594001a_rev1

DIGITAL(MEDIA PROCESSOR) SCHEMATIC DIAGRAM

2-11

2-12

Summary of Contents for DR-MV1SUS

Page 23: ... No YD006 1 23 ...