(No.YF108)2-13

2-14(No.YF108)

ANA_RST

C3209

0.1

VI3

C3210

0.1

V_OUT

RA3202

10

1

2

3

4

8

7

6

5

REG_3.1V

MPGVSYNC

R3213

12k

C3203

0.01

VI1

Y_OUT

C3206

0.1

C_OUT

C3224

1

DV2OUT5

C3213

OPEN

VI5

DV2OUT6

ANA_CLK

R3214

2.7k

C3208

1

VI7

VDCVF

VI4

REG_2.5V

C3216

0

.1

R3217

820

ASPECT

R3208

100

DV2OUT2

C3220

4.7

C3201

0.01

C3204

0.01

ANA_OUT

C3202

0.01

PSCTL

R3219

1.5k

MPGHSYNC

R3215

2.7k

C3207

0.01

C3215

OPEN

GND

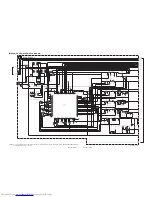

IC3201

JCP8075

1

NC1

2

NC1

13 NC1

14 NC1

54 VSS

3

RST

97 CSO0

55 CSO1

133 CSO2

99 CSO3

4

YSO0

98 YSO1

134 YSO2

56 YSO3

5

VDD(I/O)

100 OUTH

135 OUTV

6

OUTH2

57 OUTV2

101 ZCNT

7

SDOUT

58 VDD(CORE)

102 VSS

136 CLK

8

SDIN

59 SCLK

103 CS

9

VC0

60 VC1

137 VC2

104 VC3

10 BLK1

61 BLK2

138 BLK3

11 HDOUT

62 VDOUT

105 CLKOSD

139 HDCVF

12 VDCVF

63 VSS

161 NC2

162 NC2

163 NC2

164 NC2

165 NC2

15

NC1

26

NC1

27

NC1

28

NC1

106

VDD(I/O)

107

CSYNC

140

SCANMODE

65

SCANEN

16

ADDATEST

141

VCC

66

IPTEST

17

VDD(I/O)

108

HRP1

67

HRP2

18

VDD(CORE)

142

WYSI0

109

WYSI1

19

WYSI2

68

WYSI3

143

MONI1

110

MONI2

20

VDD(CORE)

69

VSS

144

WCLK

21

WCSI0

70

WCSI1

111

WCSI2

71

WCSI3

22

WINV

112

WINH

145

SDR_ONH

23

VDD(I/O)

146

VSS

72

VDD(CORE)

25

RESVD

24

RESHD

73

AMUTE

113

SCANI1

114

SCANI2

74

VSS

166

NC2

167

NC2

168

NC2

169

NC2

170

NC2

39

NC2

40

NC1

41

NC1

52

NC1

76

VDD(CORE)

29

SCANI3

30

VSS(8DA)

115

VDD(8DA)

147

COUT

116

VREF2

77

CBOUT

148

COMP2

117

ABAR2

78

CROUT

31

IREF2

149

VDD(8DA)

118

VSS(8DA)

79

NC

32

NC

150

NC

119

NC

33

VDD(10DA)

80

VSS(10DA)

151

VREF1

81

YSOUT

34

COMP1

120

ABAR1

152

YCOUT

35

IREF1

82

CLPY

121

VYIN

83

VSS(8AD)

36

VDD(8AD)

122

VRM

153

VRL

37

VRH

84

CIN

123

VDD(8AD)

38

VSS(8AD)

85

VSS

171

NC2

172

NC2

173

NC2

174

NC2

175

NC2

53

NC1

64

NC1

75

NC1

86

NC1

154

VCCQ

87

CSI0

42

CSI1

124

VSSQ

125

CSI2

88

CSI3

155

VCCQ

43

VDD(I/O)

126

CSI4

89

VSS

44

VDD(CORE)

127

CSI5

156

VSSQ

90

CSI6

45

CSI7

128

INH

91

INV

46

VDD(CORE)

157

VSS

129

VDD(I/O)

158

VCC

47

VSS

92

YSI0

48

VDD(CORE)

93

YSI1

130

VSSQ

49

YSI2

94

YSI3

131

VCCQ

50

YSI4

95

YSI5

159

VSSQ

132

YSI6

51

YSI7

96

VDD(I/O)

160

VCCQ

176

NC2

177

NC2

178

NC2

179

NC2

180

NC2

DV2OUT0

C3214

OPEN

R3212

18k

VI6

VI0

C3205

0.1

R3216

820

L3701

DV2OUT4

R3218

1.5k

C3218

0.01

VI2

DV2OUT3

RA3201

10

1

2

3

4

8

7

6

5

C3211

1

DV2OUT7

HDCVF

ANA_CS

L3201

NQR0129-002X

C3212

SHORT

0.1

C3217

DV2OUT1

ANA_IN

REG_4.8V

MPGFLD

OUTV2

R3211

R3210

R3202

R3203

R3204

R3205

R3206

R3207

R3201

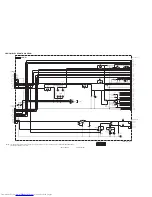

IC3202

MB90099PFV137EX

20

HD

19

VD

18

VC0

17

VC1

16

VC2

15

BLKA

14

VC3

13

BLKB

12

TSTO

11

BLKC

10 GND

9

TEST

8

EXD

7

NC

6

SDR

5

VDD

4

RST

3

SIN

2

CS

1

SCLK

Q7801

UMX1N-W

2

1

4

5

3

6

R7804

2.2k

R7803

620

R7805

12k

R7807

8.2k

C7804

1/16

R7810

12k

C7805

1/16

Q7802

UMX1N-W

2

1

4

5

3

6

R7809

2.2k

R7812

8.2k

R7808

620

R7815

12k

C7806

1/16

Q7803

UMX1N-W

2

1

4

5

3

6

R7814

2.2k

R7817

8.2k

R7813

620

R7851

33k

R7853

36k

MON_G

MON_R

MON_B

R7854

33k

R7856

36k

R7857

33k

R7859

36k

R7802

8.2k

R7801

36k

C7803

1

HRP

REG+CCD

C3708

1

R3705

10k

Q3701

BC847PN-X

5

4

6

2

1

3

R3706

1.2k

R3707

2.2k

OSD_CS

DSP_RST

C3219

0.1

C3225

1

C3227

1

L3206

SHORT

C3230

OPEN

[1608]

IC3701

LA73076V-X

16

A-GND

15

Y-OUT

14

VCC_A

13

MIX-OUT

12

VCC_NVG

11

-VCC

10

ND

9

CLK-OUT

1

S_CTL

2

P-SAV-CTL

3

C-OUT

4

C-MUTE-CTL

5

C-IN

6

RIP-FIL

7

Y-IN

8

GND

C3705

0.01

R3704

68

C3707

1

C3702

2.2

C3703

4.7

C3710

0.1

R3703

68

R3702

68

L7851

SHORT

C7802

1/16

C7801

OPEN

L7801

SHORT

T

C3701

10/6.3

C7852

0.01

OSD_VD

R3209

TL3203

TL3201

TL3202

DV2CKOUT

R3220

C3706

0.01

Q3201

UMT1N-W

2

6

3

5

4

1

T

C3709

10/6.3

L3702

C3704

0.1

IC3204

R1100D251C-X

1

VOUT

2

VDD

3

GND

R3222

33

[1608]

R3221

100

L3203

SHORT

Q3202

2SC4617/QR/-X

TO MAIN IF,

TG133(CN105)

TO MAIN IF(CN103),

MPEG2,DSP MEM

(L:OUTV,OUTH=HiZ)

C

3222

3202,3204,3205

3202

3230

LAST NO.

3206

VACANT NO.

IC

3204

L

R

3221

Ω

3223,3226,3228,3229

RA

Q

3202

3203

SYMBOL NO. 3201~

L

3702

VACANT NO.

IC

3701

LAST NO.

3701

R

3701

C

3707

SYMBOL NO. 3701~

3710

Q

SYMBOL NO. 7801~

7801

VACANT NO.

LAST NO.

7806,7811,7816

R

7806

Q

7803

L

C

7817

VACANT NO.

L

C

SYMBOL NO. 7851~

7859

LAST NO.

7852,7855,7858

R

7851

7852

7851

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

10

µ

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

_0.5%

0

Ω

0

Ω

10

µ

y10564001a_rev0.1

MAIN(V I/O)

1

0

TO DSP

TO MPEG2, DSP

TO MPEG2

TO P.PRCS

TO SUB CPU

TO MAIN IF(CN101),

SUB CPU,AUDIO

TO SUB CPU

TO SUB CPU,DSP

TO OP DRV

TO SUB CPU

TO MAIN IF

(CN101,110)

TO MAIN IF

(CN101)

TO MAIN IF(CN101)

MAIN(V I/O) SCHEMATIC DIAGRAM

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked ( ) is not used.