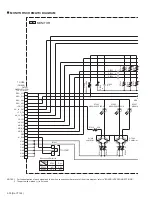

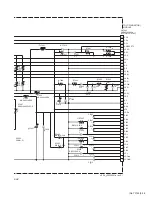

2-29(No.YF124)

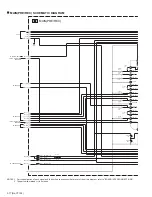

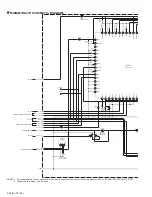

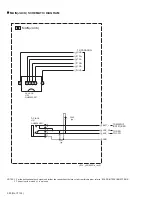

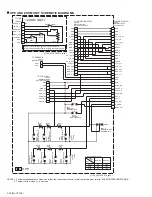

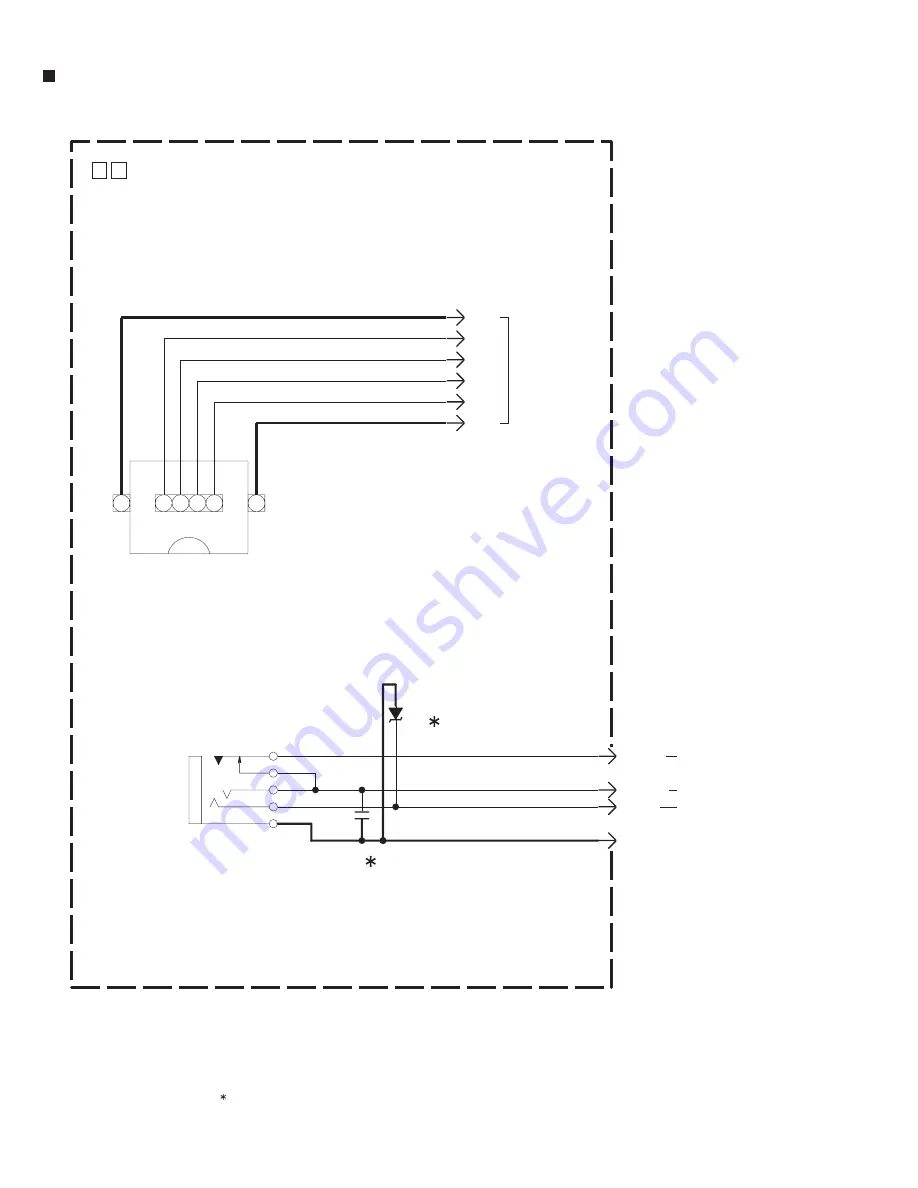

TPB+

5

BATT_+

ADP_DC

GND

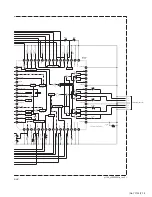

C101

ADP_L

3

4

2

5

1

6

GND

GND

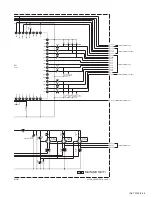

1

2

3

4

D102

TPB-

TPA+

TPA-

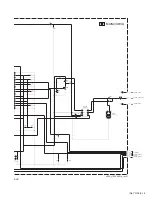

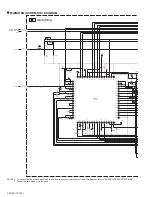

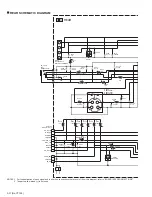

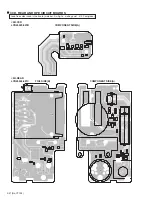

DC JACK

J101

QNA0040-001

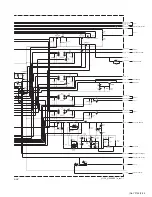

DV JACK

J102

QNZ0822-001

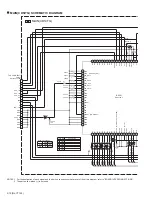

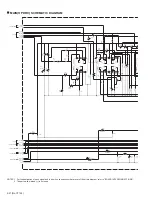

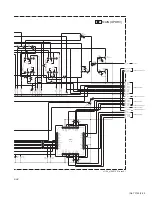

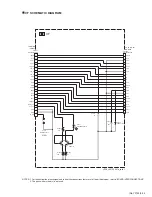

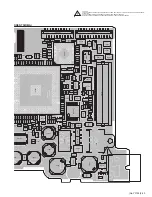

MAIN(JACK)

1

0

yf124_y40164001a_rev0.1

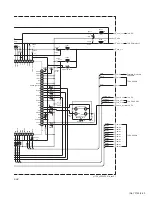

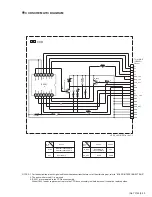

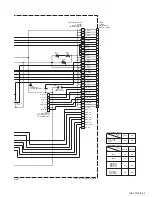

TO PARAGON

TO MAIN IF

(CN101),REG

TO REG

TO CPU

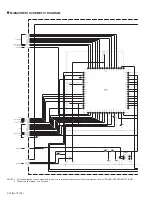

MAIN(JACK) SCHEMATIC DIAGRAM

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked (

) is not used.