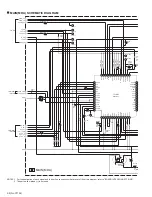

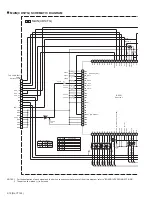

2-23(No.YF124)

!

IC6001

FA7737F

1

PGND1

2

OUT1P

3

OUT1N

4

OUT2P

5

OUT2N

6

OUT3P

7

OUT4P

8

OUT5P

9

OUT6P

10

OUT6S

11

OUT7S

12

OUT10

13

OUT11

14

OUT12

15

FB12

16

IN12-

17

PGND2

18

OUT9

19

VCC3

20

VCC1

21

DGND

22

ERR

23

RST

24

CS

25

SCLK

26

DATA

27

VDD

28

VIO9

29

VREF

30

IN8-

31

IN8+

32

IN7+

33

IN7-

34

FB7

35

IN6C-

36

FB6C

37

IN6-

38

FB6

39

IN5-

40

FB5

41

IN4+

42

IN4-

43

FB4

44

IN3+

45

IN3-

46

FB3

47

IN2-

48

FB2

49

IN1-

50

FB1

51

FB9

52

IN9-

53

GND

54

CP

55

RT

56

VIN1

57

VIN2

58

VIN3

59

VREG

60

VIN4

61

VIN5

62

SD

63

DT

64

VCC2

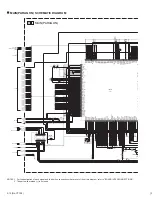

F6001

NMFZ007-2R5X-K

C6003

OPEN

C6005

1

C6706

220p

C6510

0.0047

C6405

0.01

C6305

0.1

C6103

220p

C6803 0.001

C6010

1

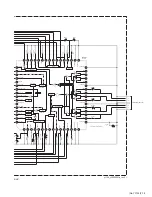

R6710

120k

R6712

560

R6005

30k

R6713

100k

C6705

0.01

R6105

CHRG_EVR

C6704

0.0047

R6714

470

TL6001

R6709

110k

C6703

OPEN

R6708

15k

R6716

8.2k

R6715

4.7k

R6513

27k

C6204

220p

R6204

8.2k

R6512

47k

C6509

0.033

R6103

8.2k

R6802

4.7k

R6803

1k

C6104

680p

C6804

0.0039

C6009 0.22

C6011

1

C6105

0.01

C6008

1

D6

RB551V

L6801

NQL365K-470X

C

C

0

C

0

Q6103

RSR025P03-X

D

G

S

R6106

100k

C

R6108

36k

R6107

24k

C6707

820p

R6717

18k

R6711

OPEN

C6007

0.1

C6006

0.1

R6110

C6107

0.022

BATT_+

BATT_CHK

C6203

0.001

TL6003

TL6002

R6007

OPEN

ADP_DC

L6002

OPEN

L6001

OPEN

L6802

OPEN

_0.5%

12k

47

µ

_0.5%

_0.5%

3.3k

MAIN(REG)

1

0

TO MAIN IF(CN101)

TO JACK

TO CPU

TO MAIN IF(CN101),

JACK

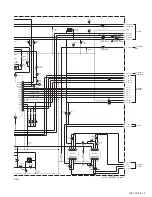

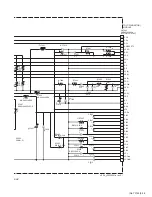

MAIN(REG) SCHEMATIC DIAGRAM

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked ( ) is not used.