2-28

5

4

3

2

1

A

B

C

D

E

F

G

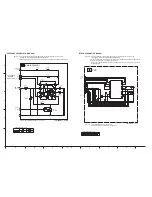

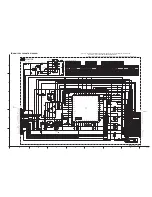

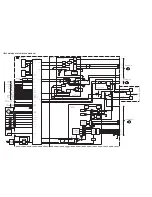

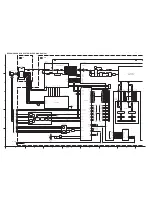

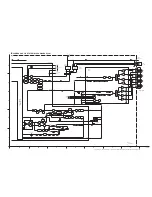

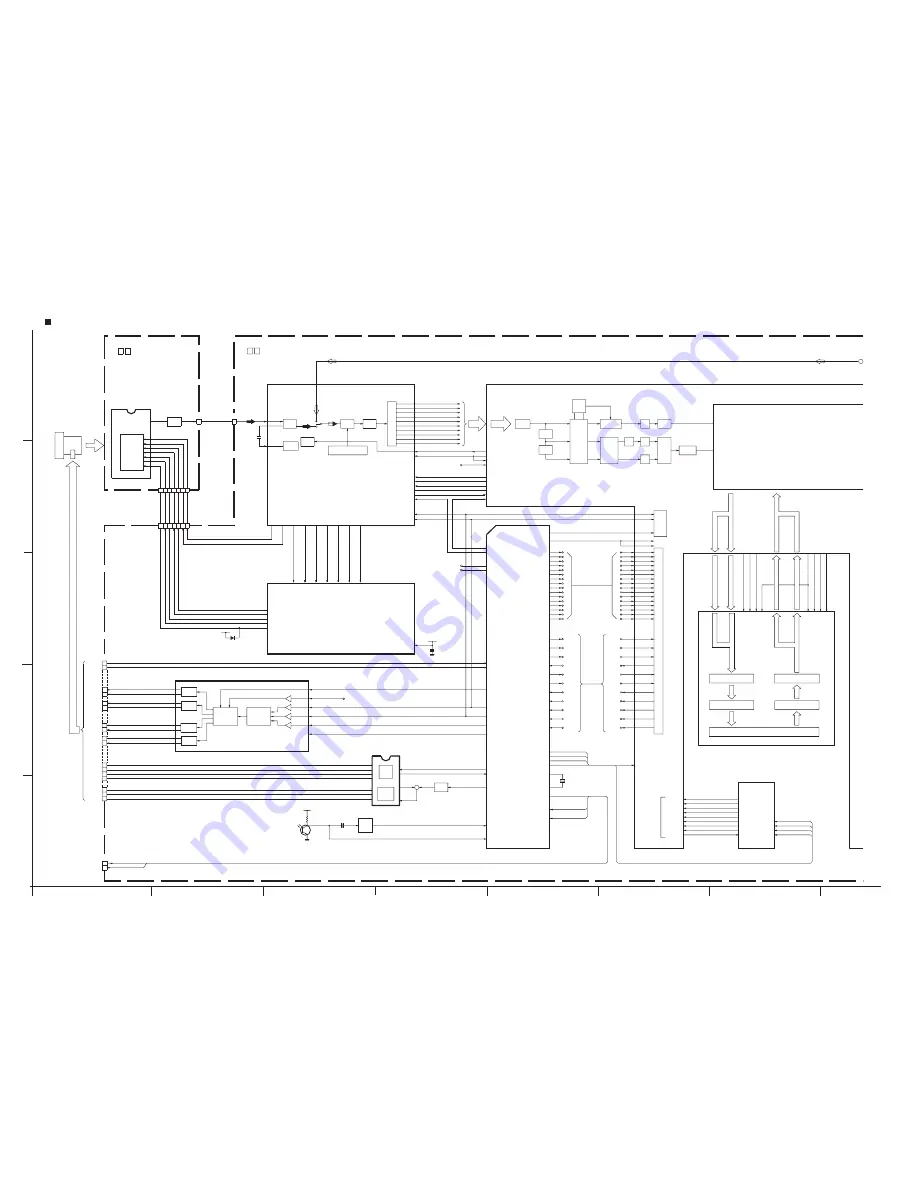

CAMERA AND Y/C SYSTEM BLOCK DIAGRAM (1/2)

SERIAL INTERFACE

C4256

R4262

3

2

1

CS

DATA

PCL

CLK

OSD_CLK

OSD_CS

OSD_DATA

DSP_REST

4

MATRIX

G

CTL

γ

G

CTL

γ

γ

WB

V/H

CTL

APT

PROCESS

SEPA

RGB

(3LINE)

Y/C

SEPA

CLAMP

OB

IH

DL

IH

7

BUS0

145

IC101(CPU)

AD0

AD0

DL

C

12

D9

AD9

AD9

AD0

AD9

AD0

6

7

11

10

9

8

LA

TCH

D3

D4

D8

D7

D6

D5

16

HD

62

17

41

1

60

CS

VD

STROB/Vgate

ID

MONI

3

4

D0

D1

64

63

SCK

Sdata

5

D2

AD0

AD1

AD2

AD3

AD4

AD8

AD7

AD6

AD5

ADCIN

44

(CDS/AGC/AD/TG)

IC5201

(TG/CDS)

PGA

CONV

A/D

C

CDS

54

51

BLKSH

CDSIN

OFFSET

DC

53

BLKFB

C5218

T. G

HDTG

VDTG

LHFO

PBLK

38

ID

DSGAT

21

CCD_CS

TL5203

TL5202

TL5201

CDS_CS

36

35

ADCLK

MAIN

0 1

25

BUS15

INTERF

A

C

E

RW

5

ASTB

6

ASTB

1

DSTB

OMT

OMT

BUSY

162

AD15

140

142

170

WAIT_L

OMT

141

98

WAIT(L)

R/W(L)

DSTB(L)

ASTB

OMT

AD15

DSTB_L

WAIT_L

BLK1

BLK2

11

13

VG

VBLK

VB

18

17

VB

VG

15

BLK1

BLK2

VG

VBLK

VB

BLK_1

BLK_2

VBLK

FRP

31

CFM

VREF0

29

FI

30

FLDCPU

VDCPU

28

HDCPU

VR

VC2

VC1

8

12

14

OSCIN

VC2

VR

VC1

CLKOSD

CLKOSD

VC_1

VC_2

CLR

16

VR

OSD I/F

104

CFM

110

VDVHS

73

V_FF

103

FI

96

VD_H

25

OSD_CLK

15

HD_H

FI

VD

HD

FRP

VDVHS

V_FF

OSD_CLK

24

OSD_DATA

DSP_REST

4

X101

71

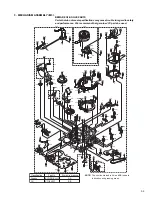

MAIN SYSTEM

70

CLOCK (16MHz)

OSD_CS

OSD_DATA

DSP_RST

X1

X2

31

OSD_CS

HD_H

V_FF

VDVHS

VD_H

124

ZOOM_SENS

FOCUS_SENS

123

26

IV1

IV2

IV3

IV4

CH1

CH2

ISUB

IV1

IV2

IV3

IV4

H1A

H2A

CH1

CH2

XSUB

7

(V_DRIVER)

C5226

REG_3.2V

6

RST

36

OSCIN

SCK3

10

SO3

9

DSP_RST

4

41

LENS_CS

IRIS_PWM

59

125

16

IRIS_O/C

IR_FLICK

12

R4209,C4206

LPF

+

(COMP)

-

+

32

VD

35

SCLK

SDATA

34

38

33

LATCH

GENERATOR

PULSE

SERIAL-

DECODER

PARARELLE

IC4201

AMP

REG 4.8V

+

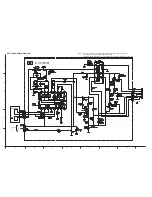

IC4201,IC4202

(F/Z/I/MDA)

MOTOR

DRIVE

AMP

HALL

AMP

LENS_MDA_CS

LENS_MDA_CLK

IR_DC

121

26

23

16

7

Z_SENS

F_SENS

CN15

30

28

24

18

17

19

FOCUS1

FOCUS4

FOCUS2

12

10

16

14

4

2

1

3

ZOOM1

ZOOM2

ZOOM4

ZOOM3

12

10

9

13

HE_IN+

HE_IN-

HE_OUT-

5

14

DRIVE+

DUMP+

DUMP- 6

FOCUS3

Q4251

IC4501(F/Z/I/MDA)

BRIDGE

DRIVER

DRIVER

BRIDGE

BRIDGE

DRIVER

DRIVER

BRIDGE

(OSD)

IC4003(DSP)

100

110

113

114

99

112

137

138

118

132

CDS_CLK

TG_CLK

AD1_CK

CAMADCK

CAMCK

CLKI

8

6

RESET

HOLE

DATA

SET

126

124

125

117

116

S03

SCK3

STD

SDCK

SLD

ADDV

HDMASK

R/W_L

DSTB_L

ASTB

R/W_L

35

36

129

240

SW30

TXD

RXD

3

94

2

TXD

RXD

140

WRITE BUFFER

WRITE RESISTOR

IE

IE

DIN7(YIN7)

DIN11(CIN3)

DIN8(CIN0)

DIN0(YIN0)

C

Y

39

32

43

7

42

C

TMC0

Y

TMY0

TMY7

TMC3

MEMORY CELL ARRAY

DOUT BUFFER

READ RESISTOR

9

RADE/RX

FCLK

WXAD

WCLK

WE

D11(COUT3)

D07(Y

OUT7)

D08(COUT0)

C

D00(Y

OUT0)

Y

42

39

37 38

34

8

10

43

7

RXAD

IC4002

(DSP)

C

FMC0

FMC3

WA

D

FMWE

Y

MCLK

RAE

FMY7

FMY0

RAD

84

87 73

81

92 96 91

67

72

59

66

88 97 90

193

194

195

192

191

188

186

187

185

V_PULSE

DSP CONTROL

INTER FACE

Q5301

BUF

IMAGE

SENSOR

CCD

H2

CN5301

5

7

14

1

2

3

4

10

13

CCD_OUT

CN22

10

IC5301

0 2 CCD

OP BLOCK

39

15

3 9 10 11 12 1314

CN5301

12 6 5 4 3 2 1

OV4

OV2

OV3

OSUB

OV1

V_DSP_CS

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

DSP_REST

CN22

V4

V3

V2

V1

SUB

H1

18

17

3

5

1

D5201

CCD-HV

IC5202(TG/CDS)

9

14

12

8

13

10

30

31

32

33

22

26

34

35

38

LENS_CLK

TO DSP

VDVHS

CLKCPU

134

RXD

RXD

161

160

159

158

157

156

155

152

151

150

149

148

147

146

79

34

8

9

11

12

13

14

16

17

18

20

21

22

23

24

C

(MEMORY)

CLKOUT

169

13

RE

FMRE

95

IC4001(DSP)

(DSP)

a

V_PB_C

7

8

TXD

RXD

CN25

TXD

RXD

JIG_CONN.

WHITE

(

BALANCE

)

SENSOR