(No.YF139)2-17

2-18(No.YF139)

SDR_DQ13

SDR_A8

SDR_DQ2

SDR_A5

SDR_DQ24

SDR_A2

SDR_DQ28

PMA14

PMA3

SDR_A1

SDR_DQ21

PMD5

SDR_DQ18

SDR_DQ19

SDR_BA0

SDR_DQ20

SDR_DQ29

SDR_A9

PMD2

PMA20

SDR_A2

SDR_DQ28

SDR_RAS

SDR_DQ10

PMD10

SDR_DQ11

SDR_A12

SDR_A11

SDR_A1

SDR_DQ10

XPMWE

PMA11

SDR_DQ5

SDR_DQ6

PMA12

SDR_DQ12

SDR_DQ17

SDR_CAS

PMA6

SDR_A10

PMA1

SDR_DQ13

SDR_RAS

SDR_DQ3

PMA8

PMA13

SDR_DQM0

SDR_CS0

SDR_CKE

SDR_DQM2

SDR_DQ16

SDR_DQ26

SDR_DQ30

SDR_DQ19

PMD13

SDR_CAS

SDR_DQ21

SDR_DQM2

PMD15

SDR_DQ12

SDR_A9

SDR_DQ30

SDR_A6

SDR_DQ25

PMA5

SDR_DQ24

SDR_DQ3

SDR_DQ25

SDR_A3

SDR_DQ22

SDR_DQ22

SDR_DQ14

SDR_DQ31

PMA4

PMD6

SDR_DQ19

PMD3

PMA15

SDR_DQ1

PMD12

SDR_BA1

SDR_DQ30

PMD0

SDR_A6

SDR_BA1

PMA2

SDR_A4

PMD11

SDR_DQ8

SDR_DQ28

SDR_DQ6

SDR_DQ7

PMA9

SDR_DQ4

XPMOE

PMD9

PMA7

SDR_DQM1

SDR_DQ8

SDR_DQM3

SDR_DQ17

SDR_DQM1

SDR_A10

SDR_DQ1

PMA21

SDR_DQ15

SDR_DQ27

SDR_DQ26

SDR_DQ25

PMD14

SDR_DQ26

SDR_DQ22

SDR_A7

SDR_DQ15

SDR_DQ4

PMD7

SDR_DQM3

SDR_DQ23

PMA19

PMA16

SDR_DQ23

SDR_A4

PMD4

SDR_BA0

SDR_DQ11

SDR_CKE

SDR_DQ29

SDR_DQ21

SDR_DQ20

SDR_A5

SDR_A7

PMD1

SDR_WE

SDR_DQ18

SDR_DQ7

SDR_DQM0

SDR_CS0

SDR_DQ9

SDR_DQ31

PMA18

SDR_DQ27

SDR_DQ9

PMA10

SDR_A11

SDR_DQ5

SDR_A0

SDR_DQ0

SDR_WE

SDR_DQ16

SDR_DQ18

SDR_DQ31

SDR_DQ2

PMA17

SDR_A3

SDR_DQ27

SDR_DQ14

SDR_DQ23

SDR_DQ20

SDR_CLK

SDR_DQ24

PMD8

SDR_A8

SDR_DQ29

XPMWE

PMA3

PMD11

PMA21

PMA11

PMA19

PMD13

PMA1

PMD4

PMA2

PMA4

PMA16

PMA6

PMD15

PMD9

PMA13

PMD1

PMA7

PMD3

PMD0

PMA14

PMA15

PMA8

PMD6

PMA5

PMA17

PMD2

PMA10

PMA20

XPMOE

PMD5

PMD10

PMD8

PMA12

PMD12

PMD14

PMA9

PMD7

PMA18

XPMCS7

XUSB_CS0

SDR_DQ17

SDR_DQ16

SDR_CLK

SDR_A0

SDR_DQ0

PMA1

PMD1

PMD13

XPMCS7

PMD2

PMA7

PMD12

PMA6

PMD15

PMA21

XPMOE

PMD6

PMA3

PMA16

PMA4

PMA5

PMD5

PMA11

PMA13

XPMWE

PMD9

PMD0

PMA17

PMD10

PMA10

PMA19

PMA8

PMD8

PMA18

PMD7

PMD11

PMA14

PMD14

PMD4

PMA15

PMA20

PMA12

PMA2

PMA9

PMD3

XUSB_CS0

SDR_A12

SDR_WE

SDR_DQ15

SDR_A3

C4307

0.01

C4306

0.001

C4308

0.1

SDR_DQM3

SDR_DQ26

PMD11

SDR_DQ24

SDR_A0

SDR_DQ1

SDR_CKE

SDR_DQ13

PMA1

PMA16

SDR_DQM2

C4310

0.1

PMA21

SDR_BA0

SDR_A12

SDR_DQ11

SDR_A5

PMA17

SDR_DQ10

PMA2

SDR_A10

SDR_A4

SDR_DQ8

PMA18

PMA12

PMD3

SDR_DQ28

SDR_DQ22

PMA10

PMA13

PMA7

SDR_CAS

SDR_DQ3

PMD0

SDR_DQ19

SDR_CLK

SDR_DQ9

SDR_DQM1

PMA6

SDR_DQ29

SDR_DQ30

PMA15

SDR_DQ25

SDR_A2

PMA4

GND

SDR_DQ0

SDR_A7

PMA20

SDR_DQ4

SDR_DQ12

SDR_DQM0

PMD2

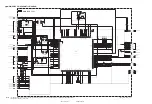

IC4303

K4S56323LF-HN75

[256M FBGA]

46 VDD

75 DQO

5

VDDQ

58 DQ1

90 DQ2

3

VSSQ

73 DQ3

89 DQ4

11 VDDQ

72 DQ5

57 DQ6

4

VSSQ

71 DQ7

56 VDD

85 DQM0

70 WE_

55 CAS_

84 RAS_

69 CS_

54 BA0

68 BA1

52 A10/AP

67 A0

82 A1

51 A2

36 A3

60 VDD

81 VDD

65 DQ16

29 VDDQ

49 DQ17

64 DQ18

32 VSSQ

77 DQ19

63 DQ20

59 VDDQ

76 DQ21

48 DQ22

44 VSSQ

61 DQ23

87 VDDQ

66 DQM2

40 NC

50 NC

88 VDDQ

86

VSSQ

53

NC

21

DQM3

35

NC

80

VSSQ

16

DQ24

79

VDDQ

33

DQ25

1

DQ26

74

VSSQ

18

DQ27

2

DQ28

78

VDDQ

19

DQ29

34

DQ30

62

VSSQ

20

DQ31

41

VSS

45

VSS

7

A4

22

A5

37

A6

8

A7

23

A8

39

A9

83

A11

38

A12

24

CKE

9

CLK

10

DQM1

25

NC

31

VSS

26

DQ8

47

VDDQ

42

DQ9

27

DQ10

13

VSSQ

14

DQ11

28

DQ12

17

VDDQ

15

DQ13

43

DQ14

12

VSSQ

30

DQ15

6

VSS

SDR_DQ18

PMA14

SDR_DQ27

SDR_DQ23

REG_3.1V

PMD10

SDR_DQ20

PMA8

PMD12

SDR_DQ31

SDR_DQ6

SDR_DQ21

SDR_BA1

PMD9

SDR_DQ14

SDR_A9

PMA3

PMD15

SDR_DQ7

PMD1

PMD5

SDR_A6

SDR_DQ16

PMD8

SDR_DQ2

PMA5

PMD4

PMD14

SDR_A8

PMA19

SDR_DQ17

PMA9

SDR_CS0

PMD13

SDR_DQ5

PMA11

PMD7

SDR_A11

C4309

0.01

SDR_RAS

SDR_A1

PMD6

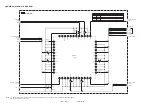

C4303

0.1

SDR_VDD

L4301

NQR0129-002X

C4301

4.7

R4301

47k

L4302

OPEN

L4303

NQR0154-003X

T

C4304

OPEN

C4305

4.7

RA4301

100k

1

8

F880[2]

RA4301

100k

2

7

CF PORT POWERUP

RA4301

100k

3

6

CF PORT POWERUP

RA4302

100k

3

6

USB PORT POWERUP

RA4302

100k

1

8

CF PORT POWERUP

RA4302

100k

4

5

CF PORT POWERUP

RA4301

100k

4

5

CPU SELECT

RA4302

100k

2

7

F89E[6]

RA4304

100k

1

8

F89E[5:3]

RA4303

100k

4

5

F89E[5:3]

RA4303

100k

3

6

RESERVED

RA4303

100k

1

8

F89E[5:3]

RA4304

100k

3

6

MEMORY WIDTH FOR FLASH

01: 16bit

RA4303

100k

2

7

MEMORY WIDTH FOR FLASH

01: 16bit

RA4304

100k

4

5

F880[0]

RA4304

100k

2

7

F880[1]

XPMWE

XPMOE

XPMCS7

FLSH_RST

TL4301

TL4302

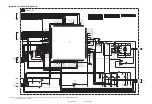

IC4302

39VF1674CB3KF40

16

A16

15

BYTE

13

VSS

14

DQ15/A-1

35

DQ7

34

DQ14

12

DQ6

33

DQ13

46

DQ5

45

DQ12

11

DQ4

32

VCC

31

DQ11

10

DQ3

44

DQ10

43

DQ2

30

DQ9

9

DQ1

29

DQ8

28

DQ0

7

OE

8

VSS

6

CE

5

A0

4

A1

3

A2

1

A3

2

A4

27

A5

26

A6

24

A7

25

A17

41

A18

23

RY/BY

40

WP/ACC

48

NC

39

RESET

22

WE

42

A20

47

A19

38

A8

21

A9

37

A10

36

A11

19

A12

20

A13

18

A14

17

A15

IC4301

SP32J55BFI12D40

16

A16

15

BYTE

13

VSS

14

DQ15/A-1

35

DQ7

34

DQ14

12

DQ6

33

DQ13

46

DQ5

45

DQ12

11

DQ4

32

VCC

31

DQ11

10

DQ3

44

DQ10

43

DQ2

30

DQ9

9

DQ1

29

DQ8

28

DQ0

7

OE

8

VSS

6

CE

5

A0

4

A1

3

A2

1

A3

2

A4

27

A5

26

A6

24

A7

25

A17

41

A18

23

RY/BY

40

WP/ACC

48

NC

39

RESET

22

WE

42

A20

47

A19

38

A8

21

A9

37

A10

36

A11

19

A12

20

A13

18

A14

17

A15

C4302

0.1

XUSB_CS0

C4352

1

IC4304

R1114N251B-X

1

VDD

2

GND

3

CE

4

NC

5

VOUT

C4351

1

SREG2.5V

R4302

OPEN

R4303

OPEN

[4M FLASH_MEMORY]

[2M FLASH_MEMORY]

2.5V

C

VACANT NO.

4352

L

4303

R

4303

RA

4304

IC

4304

LAST NO.

4311-4350

MAIN(DSP MEM)

1

0

yf139_y10610001a_rev0.1

TO SUB CPU

TO MPEG2,V I/O

TO DSP

TO USB HOST

TO MPEG2,DSP,

P.PRCS,USB HOST

TO DSP

TO DSP,USB HOST

TO DSP

TO MPEG2,DSP

TO MPEG2,DSP,P.PRCS

TO MPEG2,DSP,

P.PRCS,USB HOST

TO DSP,USB HOST

TO MPEG2,DSP,

P.PRCS,USB HOST

MAIN(DSP MEM) SCHEMATIC DIAGRAM

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked ( ) is not used.