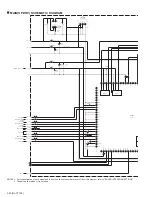

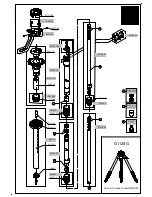

2-11(No.YF146)

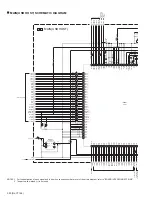

VO0

MPGFLD

XVOEN

VO1

MPGHSYNC

VO2

MPGVSYNC

VO3

VI0

VO4

VI1

VO5

VI2

VO6

VI3

VO7

VI4

VOCLK

VI5

VI6

VI7

VO0

VI0

VO1

VI1

VO2

VI2

VO3

VI3

VO4

VI4

VO5

VI5

VO6

VI6

VO7

VI7

VOCLK

MPGHSYNC

MPGVSYNC

MPGFLD

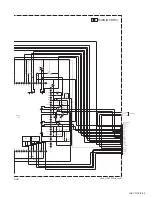

REG_1.5V_L3002

XVOEN

REG_3.1V_L3001

DV1IN7

C3008

0.1

DV2CKOUT

DV1CLKIN

REG_1.5V

VI1

XVOEN

REG_3.1V

VI2

R3030

4.7k

MPGFLD

R3040

270

VI3

C3009

0.1

R3007

10k

GND

VI4

AIBD

R3008

10k

VI5

AOBD

VI6

C3012

0.1

AIOBCK

R3009

10k

CLK27B

VI7

AIOLRCK

C3010

0.1

C3014

0.1

DV1IN0

C3013

0.01

AOMCLK

DV1IN1

C3011

0.01

C3015

0.01

R3001

10k

C3016

0.1

DV1IN2

R3035

10k

MPEG_RST

C3005

0.1

DV1IN3

R3002

10k

PLLSTOP

R3036

10k

DV1IN4

L3001

NQR0129-002X

C3006

0.01

R3004

10k

MPGHSYNC

DV1IN5

R3029

4.7k

L3002

NQR0154-003X

R3039

MPGVSYNC

C3007

0.01

DV1IN6

L3005

NQR0006-001X

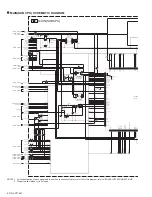

IC3001

UPD61152F1-A03

213

VI0

75

VI1

149

VI2

76

VI3

150

VI4

77

VI5

151

VI6

78

VI7

211

VIHSYNC

148

VIVSYNC

74

VIFLD/VIVLD

152

VICLK

67

VO0

206

VO1

68

VO2

207

VO3

142

VO4

69

VO5

143

VO6

70

VO7

141

VOCLK

66

XVOEN

140

VOHSYNC

205

VOVSYNC

138

AILRCK

204

AIBCK

65

AIBD

203

AIOLRCK

64

AIOBCK

137

AIOBD

136

ATX

139

AIMCLK

63

AOMCLK

174

SIREQ

23

SICLK/SISTB

173

SISYNC

27

SIVLD

101

SI0

172

SI1

24

SI2

102

SI3

25

SI4

10

SI5

72

STCLK

210

PWM

209

PSTOP

38

JMOD

115

NMOD/JTMS

116

NCLK/JTCLK

114

XNRST/XJTRST

37

NDI/JTDI

182

NDO/JTDO

110

GPIO0

179

GPIO1

33

GPIO2

111

GPIO3

34

GPIO4

112

GPIO5

243

VDD3

241

VDD3

240

VDD3

237

VDD3

233

VDD3

261

VDD3

264

VDD3

269

VDD3

270

VDD3

198

VDD1

247

VDD1

251

VDD1

242

VDD1

239

VDD1

234

VDD1

171

VDD1

232

VDD1

226

VDD1

224

VDD1

158

VDD1

156

VDD1

255

VDD1

262

VDD1

268

VDD1

271

VDD1

216

VDD1

265

VDD1

222 VDDR

225 VDDR

227 VDDR

230 VDDR

169 VDDR

199 VDDH

256 VDDH

254 VDDH

252 VDDH

248 VDDH

246 VDDH

249 GND

61 GND

62 GND

201 GND

202 GND

214 GND

215 GND

263 GND

267 GND

236 GND

231 GND

180 GND

184 GND

181 GND

260 GND

266 GND

258 GND

218 GND

223 GND

250 GND

229 GND

244 GND

238 GND

235 GND

272 GND

155 GND

220 GND

160 GND

163 GND

228 GND

168 GND

170 GND

259 GND

200 GND

257 GND

253 GND

185 GND

208 GND

71 GND

79 GND

212 GND

178 GND

147 PVDD

73 PVDD

146 PGND

145 PGND

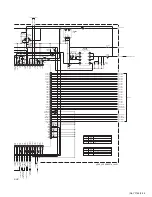

183 CSCLK

40 CSDI

41 CSDO

217 VDDR

273 VDDR

219 VDDR

221 VDDR

R3003

10k

VI0

R3042

10

R3043

10

R3044

10

R3045

10

R3034

4.7k

R3033

4.7k

R3031

4.7k

SREG2.5V

OPEN

C3001

[2125]

OPEN

C3003

[2125]

T

C3004

10/6.3

R3032

47k

OPEN

C3002

[2125]

TL3001

RA3001

180

1

2

3

4

8

7

6

5

RA3002

180

2

1

4

3

7

8

5

6

R3046

0

Ω

0

Ω

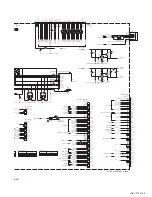

MAIN(MPEG2)

1

0

TO P.PRCS

TO DSP

TO V I/O,DSP MEM

TO MAIN IF

(CN103),P.PRCS

TO V I/O

TO DSP

TO V I/O,DSP

TO AUDIO

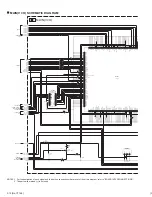

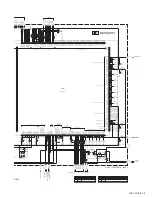

MAIN(MPEG2) SCHEMATIC DIAGRAM

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked ( ) is not used.