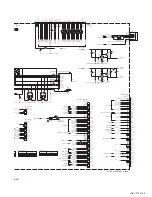

2-13(No.YF146)

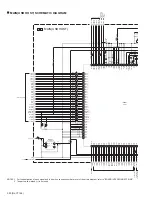

(N

VI7

VI5

VI2

VI3

VI6

VI4

VI0

VI1

OSD_VD

VI6

VI3

0.1

C3217

L3201

NQR0129-002X

R3206

R3209

MPGFLD

C3205

0.1

R3207

R3204

VI0

GND

R3208

100

TL3203

DV2OUT2

C3203

0.01

R3201

C3220

4.7

L3203

NQR0129-002X

R3211

VI7

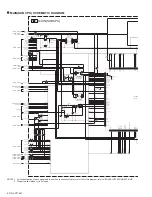

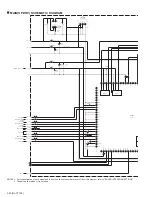

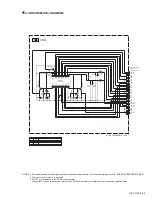

IC3202

MB90099PFV139EX

20

HD

19

VD

18

VC0

17

VC1

16

VC2

15

BLKA

14

VC3

13

BLKB

12

TSTO

11

BLKC

10 GND

9 TEST

8 EXD

7 NC

6 SDR

5 VDD

4 RST

3 SIN

2 CS

1 SCLK

DV2OUT4

VI4

C3201

0.01

R3210

C3225

1

DV2CKOUT

C3204

0.01

PSCTL

RA3202

10

1

2

3

4

8

7

6

5

SREG2.5V

ANA_CS

R3220

VI2

C3227

1

DV2OUT7

ANA_OUT

MPGVSYNC

REG_3.1V

C3224

1

TL3202

C3216

0.1

C3202

0.01

DV2OUT1

VI5

DV2OUT5

MPGHSYNC

DV2OUT3

TL3201

DV2OUT6

ANA_IN

REG_14V

RA3201

10

1

2

3

4

8

7

6

5

ANA_CLK

IC3204

R1100D251C-X

1

VOUT

2

VDD

3

GND

OSD_CS

ANA_RST

R3203

C3218

0.01

VI1

DSP_RST

DV2OUT0

REG_4.9V

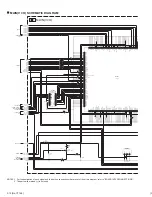

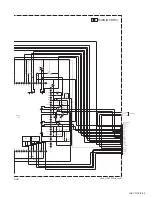

IC3201

JCP8075

1

NC1

2

NC1

13 NC1

14 NC1

54 VSS

3

RST

97 CSO0

55 CSO1

133 CSO2

99 CSO3

4

YSO0

98 YSO1

134 YSO2

56 YSO3

5

VDD(I/O)

100 OUTH

135 OUTV

6

OUTH2

57 OUTV2

101 ZCNT

7

SDOUT

58 VDD(CORE)

102 VSS

136 CLK

8

SDIN

59 SCLK

103 CS

9

VC0

60 VC1

137 VC2

104 VC3

10 BLK1

61 BLK2

138 BLK3

11 HDOUT

62 VDOUT

105 CLKOSD

139 HDCVF

12 VDCVF

63 VSS

161 NC2

162 NC2

163 NC2

164 NC2

165 NC2

15

NC1

26

NC1

27

NC1

28

NC1

106

VDD(I/O)

107

CSYNC

140

SCANMODE

65

SCANEN

16

ADDATEST

141

VCC

66

IPTEST

17

VDD(I/O)

108

HRP1

67

HRP2

18

VDD(CORE)

142

WYSI0

109

WYSI1

19

WYSI2

68

WYSI3

143

MONI1

110

MONI2

20

VDD(CORE)

69

VSS

144

WCLK

21

WCSI0

70

WCSI1

111

WCSI2

71

WCSI3

22

WINV

112

WINH

145

SDR_ONH

23

VDD(I/O)

146

VSS

72

VDD(CORE)

25

RESVD

24

RESHD

73

AMUTE

113

SCANI1

114

SCANI2

74

VSS

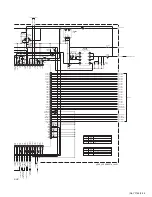

16

NC2

15

VCCQ

87

CSI0

42

CSI1

124

VSSQ

125

CSI2

88

CSI3

155

VCCQ

43

VDD(I/O)

126

CSI4

89

VSS

44

VDD(CORE)

127

CSI5

156

VSSQ

90

CSI6

45

CSI7

128

INH

91

INV

46

VDD(CORE)

157

VSS

129

VDD(I/O)

158

VCC

47

VSS

92

YSI0

48

VDD(CORE)

93

YSI1

130

VSSQ

49

YSI2

94

YSI3

131

VCCQ

50

YSI4

95

YSI5

159

VSSQ

132

YSI6

51

YSI7

96

VDD(I/O)

160

VCCQ

176

NC2

177

NC2

178

NC2

179

NC2

180

NC2

ASPECT

C3219

0.1

TL3204

R3202

R3205

Q3202

2SC4617/QR/-X

R3223

R3224

(1608)

SREG1.8V

R3225

open

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

100

33

(L:OUTV,OUTH=HiZ)

MAIN(V I/O)

1

0

TO DSP

TO MPEG2,

DSP

TO MPEG2

TO SUB CPU

TO MAIN IF(CN101),

SUB CPU,AUDIO

TO SUB CPU

TO OP DRV

TO MAIN IF

TO MPEG2,

DSP MEM

TO USB HOST

TO SUB CPU,

DSP

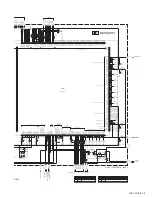

MAIN(V I/O) SCHEMATIC DIAGRAM

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked ( ) is not used.