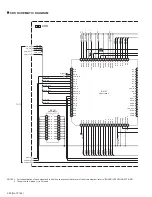

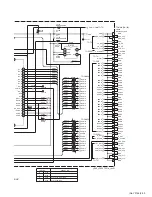

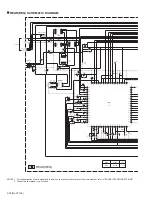

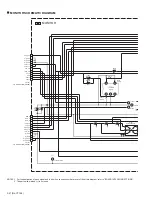

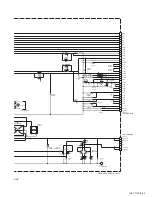

(No.YF146)2-38

[-]

[D]

[T]

[+]

REG-CCD

SJIG_RST

DRV_3.3V

DATA_OUT

CAM_3.1V

REG_1.5V

REG_4.9V

ADP_L

CHRG_EVR

GND

D_BATT

REG_1.2V

T_BATT

CLK_OUT

REG_3.1V

AL_3.1V

REG_CS

I_MTR

UNREG

V_BATT

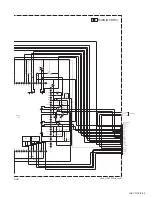

R601

10k

R602

3.3k

TP4

TP3

TP1

LY34726-001A

TP2

D601

EMZ6.8N-X

1

2

3

BATT+

BATT_CHK

R603

0

C601

0.1

C602

OPEN

C603

0.1

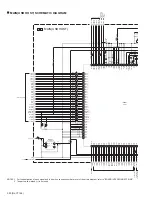

CN6001

QGF0508F1-53X

1

GND

2

GND

3

REG_3.1V

4

REG_3.1V

5

REG_3.1V

6

GND

7

CAM_3.1V

8

CAM_3.1V

9

GND

10

REG_4.9V

11

REG_4.9V

12

REG_4.9V

13

GND

14

GND

15

REG_1.5V

16

REG_1.5V

17

REG_1.5V

18

GND

19

GND

20

REG_1.2V

21

REG_1.2V

22

REG_1.2V

23

GND

24

DRV_3.3V

25

DRV_3.3V

26

DRV_3.3V

27

GND

28

AL_3.1V

29

GND

30

UNREGCHK

31

GND

32

REG+CCD

33

GND

34

REG-CCD

35

GND

36

ADP_L

37

GND

38

T_BATT

39

V_BATT

40

GND

41

I_MTR

42

SJIG_RST

43

GND

44

DATA_OUT

45

CLK_OUT

46

GND

47

REG_CS

48

CHRG_EVR

49

DC_CHEK

50

KEY_B

51

D_BATT

52

GND

53

GND

D602

UDZS16B-X

REG+CCD

R605

39k

R604

150k

C604

OPEN

DC_CHEK

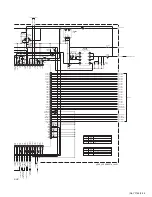

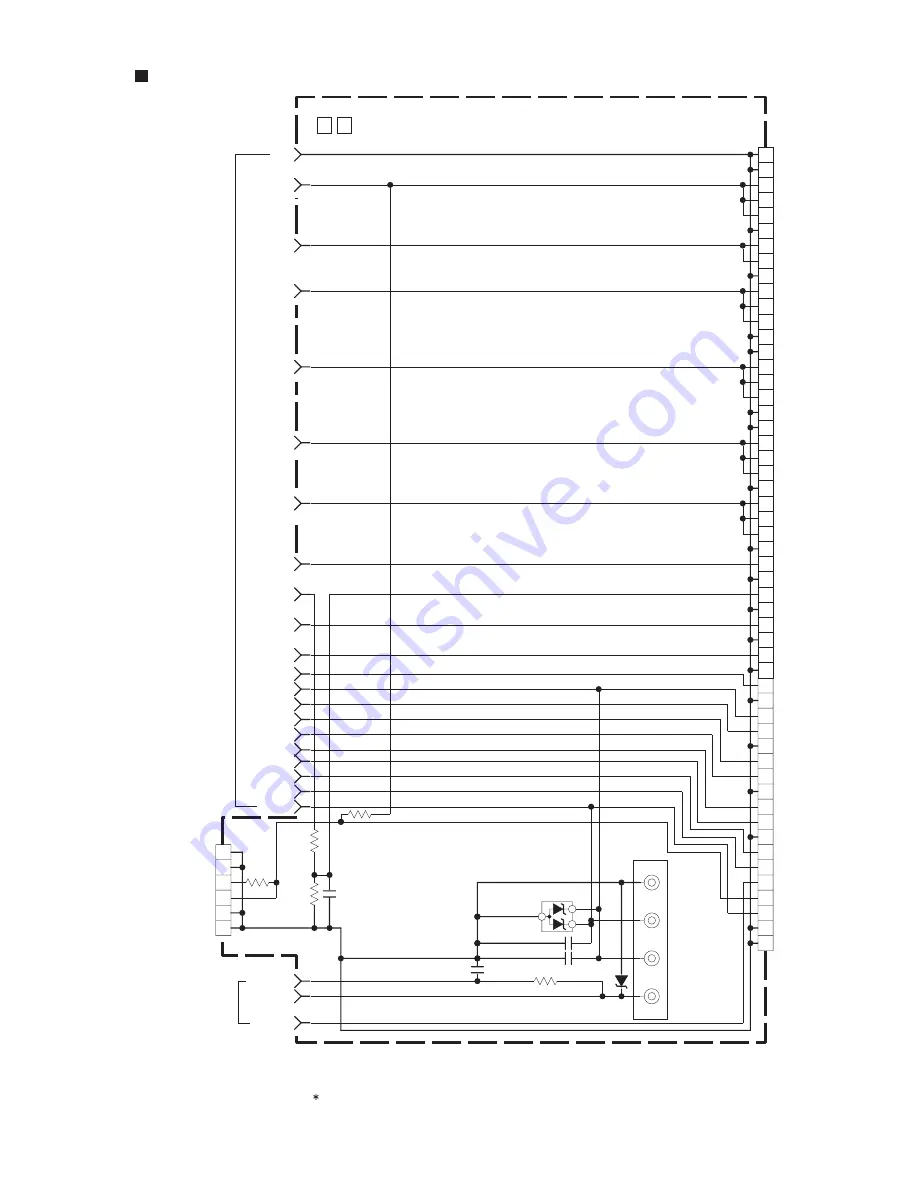

CN6002

QGF0534F2-06X

1

GND

2

GND

3

HARF_SW

4

FULL_SW

5

GND

6

GND

BATTERY TERM

_0.5%

_0.5%

yf146_y40166001a_rev0.1

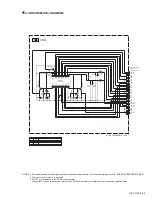

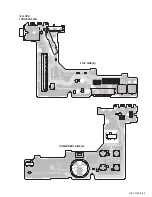

REAR(REAR IF)

5

0

TO TRIG SW

TO REG

TO REG

TO MAIN

(CN103)

REAR(REAR IF) SCHEMATIC DIAGRAM

NOTES: 1. For the destination of each signal and further line connections that are cut off from this diagram, refer to "BOARD INTERCONNECTIONS".

2. The parts with marked (

) is not used.