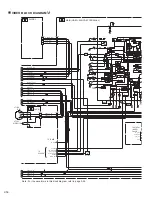

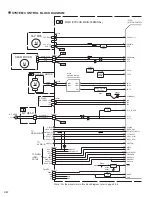

WF1

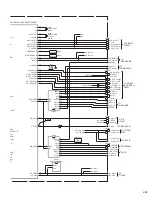

WF2

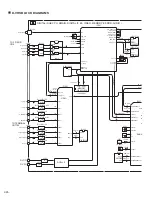

WF3

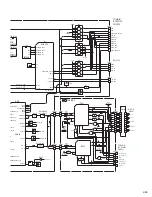

WF4

WF5

(RESET)

(SYSTEM CONTROL

VOLTAGE CONTROL)

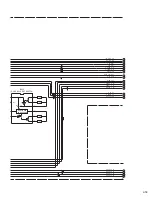

(LOADING MOTOR

MAIN (SYSCON, MAIN-TERMINAL)

IC3001

28

3

0

CN3003

MDA

8

101

CAPPWM

CFG

107

108

DPG

DFG

55

54

102

PHOTO

PC3002

PC3001

SENSOR

PHOTO

36

LMC1

38

LMC3

LMC2

37

26

27

LSB

25

LSA

LSC

TP4001

CTL.P

SENSOR

AGE

VOL T

CONTROL

DRIVE

Q3001

IC3004

3

2

CN3001

4

5

3

D.PG

D.FG

2

3

1

9

LMC1

1

Vref

LMC2

7

LDM2

2

LDM1

4

2

CN3002

1

LDM1

LDM2

1

LSB

CN3004

3

LSA

2

LSC

AR Y

ROT

ENCODER

MOTOR

6

CAP

5 5

M

DRUM MOTOR

M

M

CON1

LOADING

1

3

100

D.FF/STD.FF/HS1.FF

110

19

V.PULSE

66

RES

4

2

RESET

D3004

1

71

MODE

FWE

62

IC3002

CN2001

7

6

V/STD/HS1.FF

PULSE

V.

AL6V

1

2

HEAD

HEAD

A/C

TO

A/C

CTL

CN1

VIDEO/AUDIO

1 2

6

CTLAMPOUT

CTL HEAD(-)

CTL HEAD(+)

CTL(-)

CTL(+)

CAP_REV(L)

CAP_CTL_V

CAP_FG

DRUM_CTL_V

VIDEO_ENV

SP FG

VIDEO_ENV

TU FG

CAP REV (L)

DRUMPWM

99

A/HS2.FF

A.FF/HS2.FF

87

88

N.REC_ST(H)

H.REC_ST(H)

H.REC_ST(H)

N.REC_ST(H)

Note : For the waveforms in this block diagram, refer to page 2-56.

89

A.MUTE(H)

A.MUTE(H)

TO

AUDIO I/O

TO DIGITAL

CN7001

12

11

CN3009

HS2_FF

(HOST)

V/STD/HS1.FF

HS1_FF

For ADJ.

3

5

CN3010

FWE

SIO

6

SII

RESET

2

ES

SIO

SII

Q3013

10

9

REF30

REF5

8

7

HOST_RESET

KBUS_REQ

6

4

KBUS_CLK

KBUS_DATA

103

HOST_RESET

90

91

REF30

REF5

57

K-BUS-REQ

53

52

K-BUS-CLK

K-BUS-OUT

K-BUS-IN

51

ES

Q4002

106

HI_S_FF_REW

A/HS2.FF

AMP

IC4101

SYSTEM CONTROL BLOCK DIAGRAM

2-63