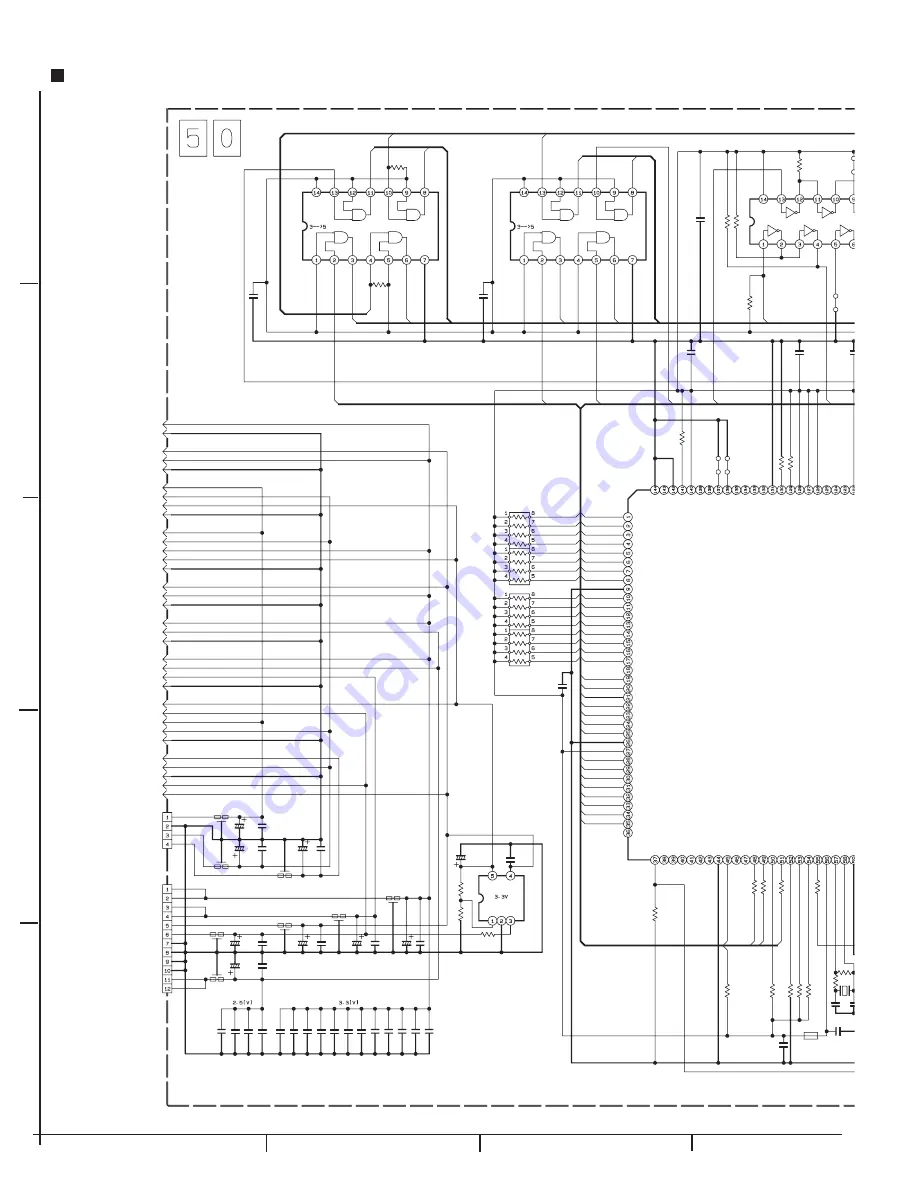

5

4

3

2

1

A

B

C

D

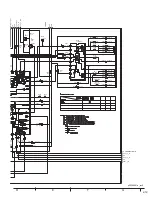

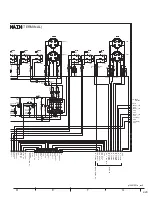

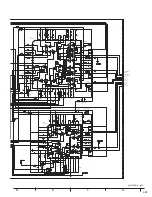

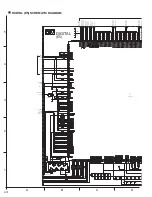

IC1

R44

C31

RA1

C35

R88

B4

C34

C33

C11

C22

RA2

RA3

RA4

CN8001

TO MAIN

(SW.REG)

CN5602

LC7

LC8

C13

C14

C16

LC6

C9

C12

LC5

C7

C10

LC4

C32

C8

C15

LC1

C1

C2

LC2

C3

C4

LC3

C5

C6

CN8002

TO MAIN

(SW.REG)

CN5601

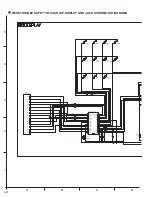

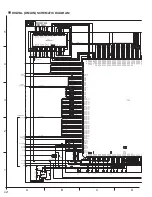

PS3.3V[D]

GND

SW5V

AUDIO[-]

TO AUDIO

GND

AL1.8V[D]

AL2.5V[D]

AL3.3V[D]

TO E5

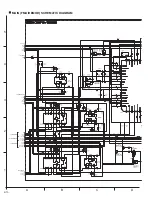

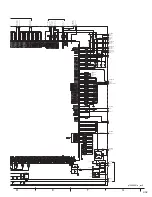

IC2

C17

C19

C18

R2

R1

C23

C20

R3

GND

SW5V

SW12V

PS3.3V[D]

PS3.3V[A]

TO VIDEO

GND

AL2.5V[D]

K1

AL3.3V[D]

TO E5 DDR

GND

AL3.3V[D]

GND

PS3.3V[A]

R46

AL3.3V[D]

GND

PS3.3V[A]

C21

SW5V

SW12V

TO DMAIN IF

GND

AL3.3V[D]

AL5V

TO SUB CPU

AL5V

SW12V

TO DMAIN

R45

AL5V

TO MEMORY

SW5V

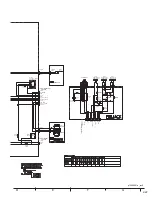

R98

R8

R89

R7

R48

R47

IC5

IC6

R4

B8

R42

R12

R10

R11

R14

R43

R5

R6

R9

B7

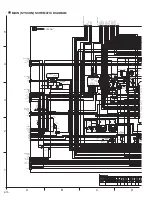

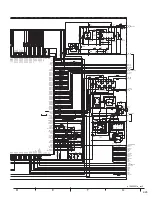

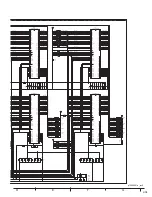

C101

C102

C103

C104

C105

C106

C107

C108

C109

C110

C111

C112

C124

C123

C122

C121

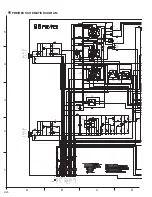

D16

D17

D18

D19

D20

D21

D22

D23

VSS

D24

D25

D26

D27

D28

D29

D30

D31

A00

A01

A02

A03

A04

A05

A06

A07

VSS

VCC

A08

A09

A10

A11

A12

A13

A14

A15

P60/A16

FSC_H

MB91154PFV107

MB91F154PFV107

MB91F155PFV107

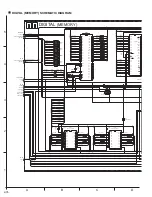

OPEN

OPEN

OPEN

/6.3

SW12V

GND

SW5V

AUDIO[-]

QGA2001F2-04W

PELN1148-223X

PELN1148-223X

/6.3

PELN1148-223X

/6.3

T

PELN1148-223X

/6.3

T

PELN1148-223X

/6.3

T

PELN1148-223X

/16

PELN1148-223X

/6.3

PELN1148-223X

/16

AL3.3V

AL3.3V

AL1.8V

AL1.8V

AL5V

PS3.3V

GND

GND

GND

AL2.5V

AL2.5V

GND

QGA2001F2-12W

SI-3012LU-X

/6.3

T

PELN0984-150Y

OPEN

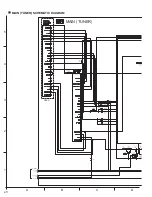

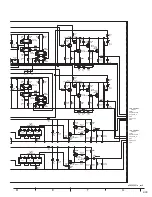

Vcc

TC74VHC05FT

OPEN

OPEN

VSS

VSS

RDY

RDX

WR0X

WR1X

CLK

MD2

MD1

MD0

RSTX

VCC

X1

X0

VCC

VC

C

DAVS

DA1

DA0

DAVS

DAVC

AVCC

AVRH

AVRL

AVSS

PK0/AN0

PK1/AN1

PK2/AN2

PK3/AN3

reserved_1

reserved_2

PK6/AN6

PK7/AN7

TEST

X0A

X1A

VSS

P81/BGRNTX

P82/BRQ

OPEN

OPEN

OPEN

SN74HCT08APW-X

SN74HCT08APW-X

ADJ

GND

VC

VIN

VO

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

OPEN

10K

0.1

10K

0.1

0.1

47

10p

10K

10K

10K

47

0.1

0.1

47

0.1

47

0.1

0.1

0.1

47

47

0.1

100

0.1

47

0.1

47

0.1

0.1

91k

150k

10p

0.1

1k

0.1

0

Ω

10k

10k

10k

10k

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

10k

BC_A[0]

SIO_UART1_TX

BC_A[1]

BC_A[2]

BC_A[3]

BC_A[4]

BC_A[5]

BC_A[6]

BC_A[7]

BC_D[15]

BC_D[14]

BC_D[13]

BC_D[12]

BC_D[11]

BC_D[10]

BC_D[9]

BC_D[8]

BC_D[7]

BC_D[6]

BC_D[5]

BC_D[4]

BC_D[3]

BC_D[2]

BC_D[1]

BC_D[0]

BC_A[8]

BC_A[9]

BC_A[10]

BC_A[11]

BC_A[12]

BC_A[13]

BC_A[14]

BC_D[0]

BC_D[1]

BC_D[2]

BC_D[3]

BC_D[4]

BC_D[5]

BC_D[6]

BC_D[7]

BC_D[8]

BC_D[9]

BC_D[10]

BC_D[11]

BC_D[12]

BC_D[13]

BC_D[14]

BC_D[15]

B_CLK

BC_WAIT

BC_WAIT

SIO_UART2_TX

LANC_RXD_H

BC_WS

BC_RS

SIO_U2_RX

KBUS_CLK

SBE1

V_SBE1

KBUS_REQ

KBUS_REQ_H

KBUS_CLK5V

SERVOREF30

SBE0

SVREF30

TXD_H

V_SBE

0

SEQ_P

REF5

REF5HZ

DIGITAL

(SUB CPU)

DIGITAL (SUB CPU) SCHEMATIC DIAGRAM

2-25