5

4

3

2

1

A

B

C

D

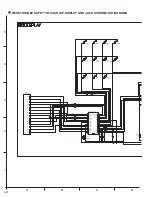

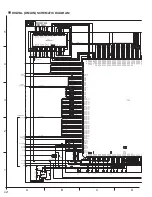

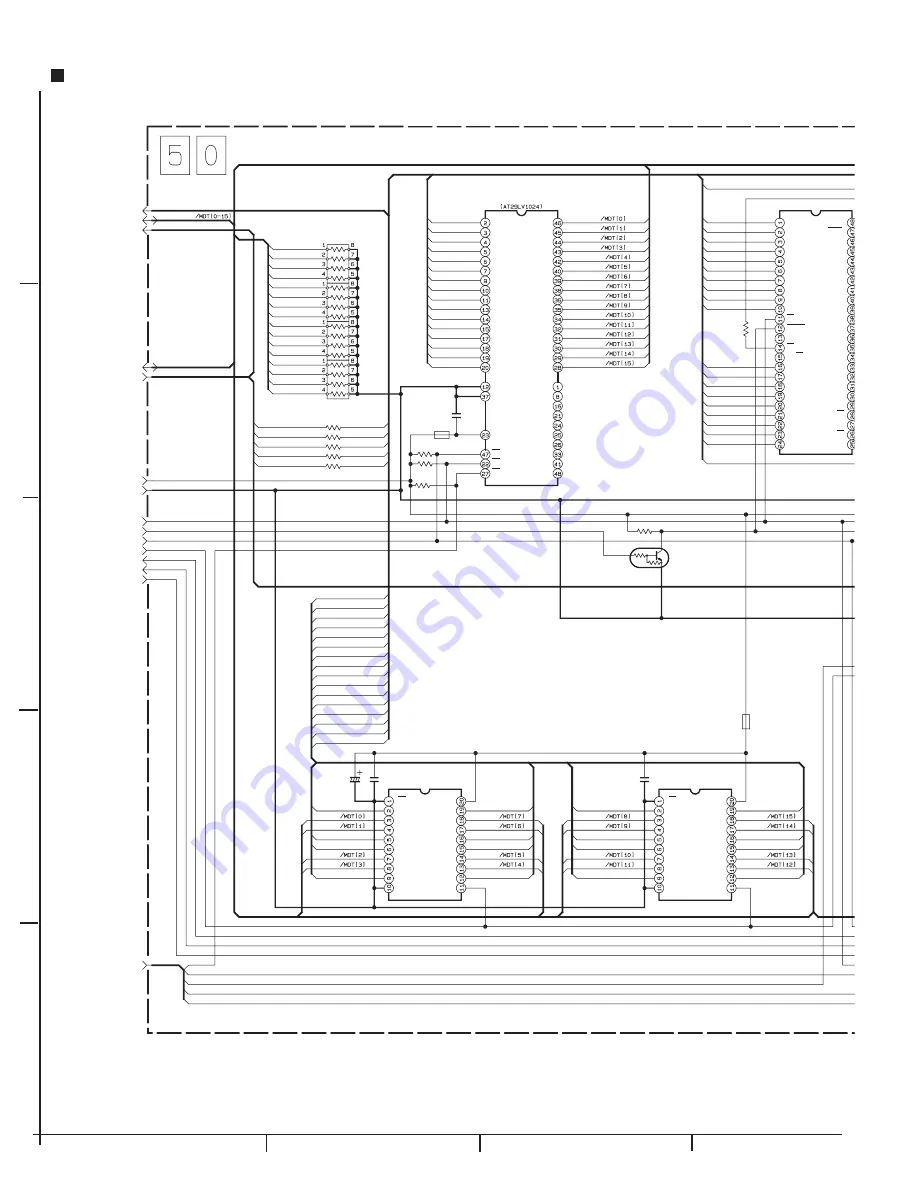

CS_L[0-4]

TO E5

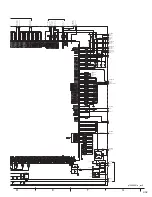

IC804

IC805

MADD[1-5]

IC802

Q801

R810

LH_AR[6-15]

TO DMAIN

MADD[6-21]/MDT[0-15]

R806

R805

R804

R803

R802

C807

C806

MADD[1-5]

C805

AL3.3V[D]

GND

DTACK_WAIT

MEDUSA_INT[L]

RA801

RA802

R807

RA803

RA804

R808

R809

K804

ALE

R811

K801

UWE[L]/UDS[L]

E5_RST[H]

MADD[6-21]/MDT[0-15]

TO E5

C801

IC801

RD/WR[L]

TO SUB CPU

TO E5

OE[L]/LDS[L]

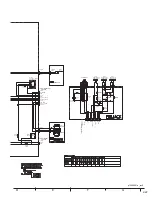

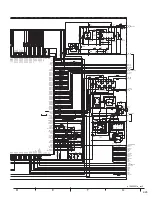

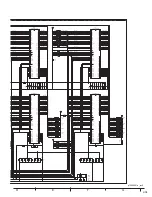

OE

Q0

D0

D1

Q1

Q2

D2

D3

Q3

GND

VCC

Q7

D7

D6

Q6

Q5

D5

D4

Q4

LE

HD74LVC373AT-X

OE

Q0

D0

D1

Q1

Q2

D2

D3

Q3

GND

VCC

Q7

D7

D6

Q6

Q5

D5

D4

Q4

LE

HD74LVC373AT-X

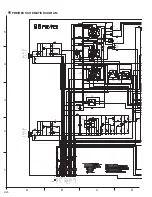

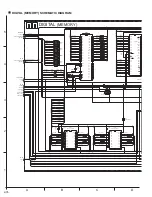

A0

CE

Vss

OE

DQ0

DQ8

DQ1

DQ9

DQ2

DQ10

DQ3

DQ11

Vcc

DQ4

DQ12

DQ5

DQ13

DQ6

DQ14

DQ7

DQ15/A-1

Vss

BYTE

A16

A15

A14

A13

A12

A11

A10

A9

A8

A19

A20

WE

RESET

N.C.

WP/ACC

RY/BY

A18

A17

A7

A6

A5

A4

A3

A2

A1

HY29LV320TT-90

DTC144EUA-X

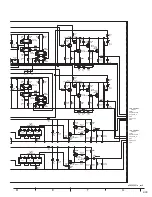

/6.3

T

NQR0129-002X

OPEN

OPEN

NQR0129-0

VSS

VSS

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

N.C.

CE

OE

WE

VCC

OPEN

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

OPEN

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

I/O8

I/O9

I/O10

I/O11

I/O12

I/O13

I/O14

I/O15

I/O16

15k

0

Ω

0

Ω

0

Ω

0

Ω

0

Ω

0.1

0.1

22

10K

10K

4.7k

10K

10K

4.7k

4.7k

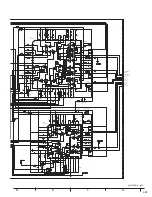

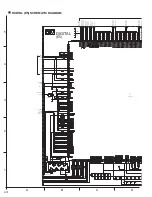

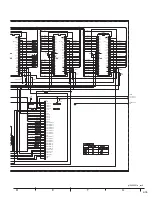

CS_L[4]

CS_L[2]

MADD[6]

MADD[7]

MADD[8]

MADD[9]

MADD[10]

MADD[11]

MADD[12]

MADD[13]

LH_AR[6]

LH_AR[7]

LH_AR[8]

LH_AR[9]

LH_AR[13]

LH_AR[12]

LH_AR[11]

LH_AR[10]

MADD[14]

MADD[15]

MADD[16]

MADD[17]

LH_AR[14]

LH_AR[15]

LH_AR[16]

LH_AR[17]

LH_AR[21]

LH_AR[20]

LH_AR[19]

LH_AR[18]

MADD[21]

MADD[20]

MADD[19]

MADD[18]

MADD[1-5]

LH_AR[16]

CS_L[1]

LH_AR[4]

LH_AR[15]

LH_AR[14]

MADD[6-21]/MDT[0-15]

LH_AR[13]

LH_AR[12]

LH_AR[11]

LH_AR[10]

LH_AR[9]

LH_AR[20]

LH_AR[21]

LH_AR[19]

LH_AR[18]

LH_AR[8]

MADD[10]

MADD[11]

CS_L[0-4]

LH_AR[7]

LH_AR[6-15]

MADD[6-21]

MADD[1-5]

LH_AR[6]

LH_AR[5]

LH_AR[3]

LH_AR[2]

LH_AR[17]

LH_AR[1]

CS_L[0]

CS_L[3]

MADD[12]

MADD[13]

MADD[6]

MADD[7]

MADD[8]

MADD[9]

MADD[21]

MADD[20]

MADD[19]

MADD[18]

MADD[17]

MADD[16]

MADD[15]

MADD[14]

LH_AR[6]

LH_AR[7]

LH_AR[8]

LH_AR[9]

LH_AR[10]

LH_AR[11]

LH_AR[12]

LH_AR[13]

LH_AR[14]

LH_AR[15]

LH_AR[16]

LH_AR[17]

LH_AR[18]

LH_AR[19]

LH_AR[20]

LH_AR[21]

MADD[1]

MADD[2]

MADD[21]

MADD[20]

MADD[3]

MADD[4]

MADD[5]

LH_AR[1]

LH_AR[16]

LH_AR[15]

LH_AR[14]

LH_AR[13]

LH_AR[12]

LH_AR[11]

LH_AR[10]

LH_AR[9]

LH_AR[8]

LH_AR[7]

LH_AR[6]

LH_AR[5]

LH_AR[4]

LH_AR[3]

LH_AR[2]

LH_AR[1]

LH_AR[2]

LH_AR[3]

LH_AR[4]

LH_AR[5]

MADD[19]

MADD[18]

MADD[17]

MADD[16]

MADD[15]

MADD[14]

MADD[13]

MADD[12]

MADD[11]

MADD[10]

MADD[9]

MADD[8]

MADD[7]

MADD[6]

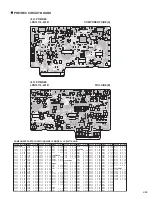

LH_AR[6-21]

LH_AR[1-21]

LH_AR[1-16]

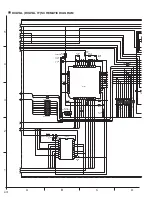

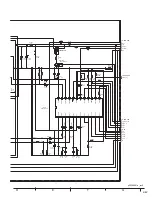

DIGITAL (MEMORY) SCHEMATIC DIAGRAM

DIGITAL

(MEMORY)

2-35