4-69

4-70

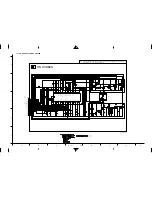

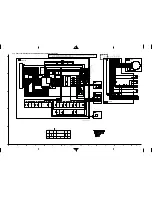

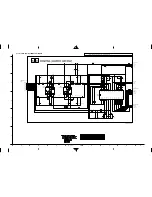

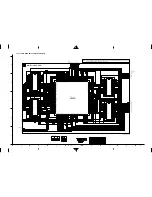

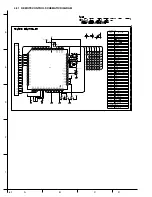

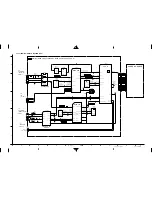

SYSTEM CONTROL BLOCK DIAGRAM (VHS)

H

G

F

E

D

C

B

A

4

5

3

2

1

4.35

(RESET)

D_R2/R1Y/FV

(TUNER/REG CTL)

(AUDIO/VIDEO CTL)

D_R2/D_R1Y/D_FV

OSC1(IN)

OSC2(OUT)

(10MHz)

(32KHz)

(SYSTEM CONTROL MICRO PROCESSOR)

VOLTAGE CONTROL)

(LOADING MOTOR

MAIN (SYSCON)

TO

VIDEO I/O SW

CN704

TO

CN7001

S3002

S.CASS

65

X1

D.FF

3

5

4

Q3002

Q3003

CLOCK

SYSTEM

64

67

69

MAIN

CLOCK

X3002

TIMER

53

52

51

S.CLK

X2

END

STAR

96

15

14

103

91

S_CASS(H)

T

SENSOR

SENSOR

X3001

CN3011

S.CLK

S.CLK

D.FF

TO

TUNER

8

7

CLK

IC3651

9

7

4

8

2

3

IC3003

49

50

FRONT

DATA1

CLK

3

2

33

79

104

IC3601

6

5

61

60

76

75

SDA

SCL

IC3001

28

3

0

CN3003

MDA

8

101

CAPPWM

CFG

107

108

DPG

DFG

55

54

102

PHOTO

PC3002

PC3001

SENSOR

PHOTO

35

LMC1

37

LMC3

LMC2

36

26

27

LSB

25

LSA

LSC

TP4001

CTL.P

SENSOR

AGE

VOL T

CONTROL

DRIVE

Q3001

IC3004

3

2

CN3001

4

5

3

D.PG

D.FG

2

3

1

9

LMC1

1

Vref

LMC2

7

LDM2

2

LDM1

4

2

CN3002

1

LDM1

LDM2

1

LSB

CN3004

3

LSA

2

LSC

AR Y

ROT

ENCODER

MOTOR

6

CAP

5 5

M

DRUM MOTOR

M

M

CON1

LOADING

1

3

. FF

100

V

110

21

98

V.PULSE

66

RES

TP3905

3

2

RESET

D3004

1

71

MODE

FWE

62

Vcc

TP3904

IC3002

D.FF

CN2001

7

6

D.FF

PULSE

V

C.SYNC/VREF

.

TP3903

AL5.8V

1

2

HEAD

HEAD

A/C

TO

A/C

CTL

CN1

VIDEO/AUDIO

1 2

6

CTLAMPOUT

CTL HEAD(-)

CTL HEAD(+)

CTL(-)

CTL(+)

(SERIAL MEMORY)

SW1

SW2

15

4

6

FULL_E_ON(L)

N.REC(L)

TO

SW.REG

I2C_CLK2

I2C_DATA2

FLY_REC(H)

CAP_REV(L)

CAP_CTL_V

CAP_FG

DRUM_CTL_V

VIDEO_ENV

S.DATA_FRSYS

S.DATA_TOSYS

S.DATA_FRSYS

V_UP(H)

OSD CS

I2C_CLK_A/V

I2C_DATA_A/V

I2C_DATA_A/V

I2C_CLK_A/V

FRONT(H)

D_TU(H)

TU_DATA

TU_CLK

SP_FG

S.DATA_TOSYS

END_SENSOR

START_SENSOR

V_UP(H)

OSD CS

I2C_DATA_A/V

I2C_CLK_A/V

VIDEO_ENV

FRONT(H)/EXP1_DATA

SUB_CS/EXP2_DATA

SUB_RESET/EXP_CLK

TU_DATA

TU_CLK

I2C_DATA2

I2C_CLK2

D_TU

DISPLAY

TU_FG

CAP REV (L)

S.DATA_FRSYS

DATA2

P.CTL(H)

FULL_E_ON

N.REC(L)

P.CTL(H)

SW_1

SW_2

DRUMPWM

C. SYNC

FLY_REC(H)

S3001

REC_SAFETY

41

REC_SAFETY

74

99

A.FF

A.MUTE(H)

A.MUTE(H)

A.FF

88

58

N.REC_ST(H)

H.REC_ST(H)

H.REC_ST(H)

N.REC_ST(H)

94

VHS(H)

VHS(H)

D_TU

9

D_VHS

10

D_TU(H)

D_VHS(H)

TO

AUDIO I/O,

VIDEO I/O SW

TO

VIDEO/AUDIO

TO

CONNECTION

CN501

TO

VIDEO/AUDIO

D_YV

11

OUT2D

14

BIL_SEL/DEC(H)

15

D_YV(H)

OUT2_D(H)

BIL_SEL/DEC(H)

BIL_SEL/DEC(H)

TO

TERMINAL

I2C DATA2

I2C CLK2

SAT_CTL

CN7503

2

3

11

Q7501

BUF

RMO

44

KBUS_DATA_IN

46

1

3

CN3014

48

KBUS_CLK

TO

CN8002

DIGITAL(ASIC IF)

KBUS_DATA_IN

KBUS_CLK

VIDEO/AUDIO

87

FLY_ON(H)

FLY_ON(H)

WF1

WF2

WF3

WF4

WF5

WF6

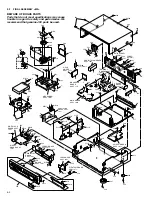

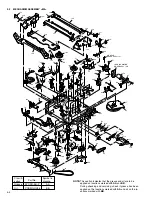

Note : For the waveforms in this block diagram, refer to page 4-63.

C3025

Timer clock

ONLY USED

FOR EU MODEL