KD-SX8350

1-34 (No.49782)

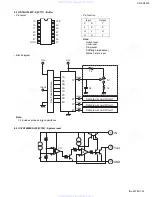

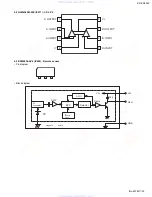

4.7 LC75873NW(IC601):LCD Driver

• Pin layout

• Block diagram

• Pin function

60 41

1 20

40

21

61

80

VDD1

VDD2

INH

OSC

CLOCK

GENERATOR

COMON

DRIVER

SEGMENT DRIVER

SHIFT REGISTOR

ADDRESS

DETECTOR

VSS

VDD

DI

CL

CE

S5

S4/P4

S3/P3

S2/P2

S1/P1

S62

S66

COM1

COM2

COM3

Pin No.

Pin name

I/O

Description

79,80

1,2,3

to 66

S1/P1 to S4/P4

S5 to S68

O

Segment outouts for displaying the display data transferred by serial data input.

The S1/P1 to S4/P4 pins can be used as generalpurpose output ports under serial data

control.

67

78

69

COM1

COM2

COM3

O

Common driver outputs.

The frame frequency f0 is given by :

f0 = (FOSC/384)Hz.

74

OSC

I/O

Oscillator connection

An oscillator circuit is formed by connecting an external resistor and capacitor to this pin.

76

77

78

CE

CL

DI

I

I

I

Serial data transfer inputs.

Connected to the controller.

CE:Chip enable

CL:Synchronization clock

DI:Transfer data

75

INH

I

Display off control input

• INH= "L"(VSS) ---Display forced off

S1/P1 to S4/P4 = "L"

(These pins are forcibly set to the segment output port function and held at

the low level.)

S5 to S68 = "L"

COM1 to COM3"L"

• INH = "H"(HDD)---Display on

However, serial data transfer is possible when the display is forced off by this pin.

Used for applying the LCD drive 2/3 bias voltage externally. Must be connected to VDD2

when a 1/2 bias drive scheme is used.

Used for applying the LCD drive 1/3 bias voltage externally. Must be connected to VDD1

when a 1/2 bias drive scheme is used.

Power supply connection. Provide a voltage of between 3.0 and 6.0V.

Power supply connection. Connect to ground.

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299