MX-G70

1-48

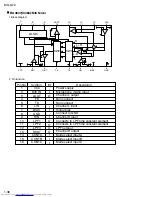

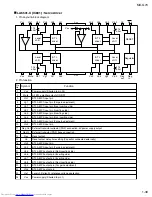

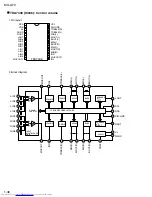

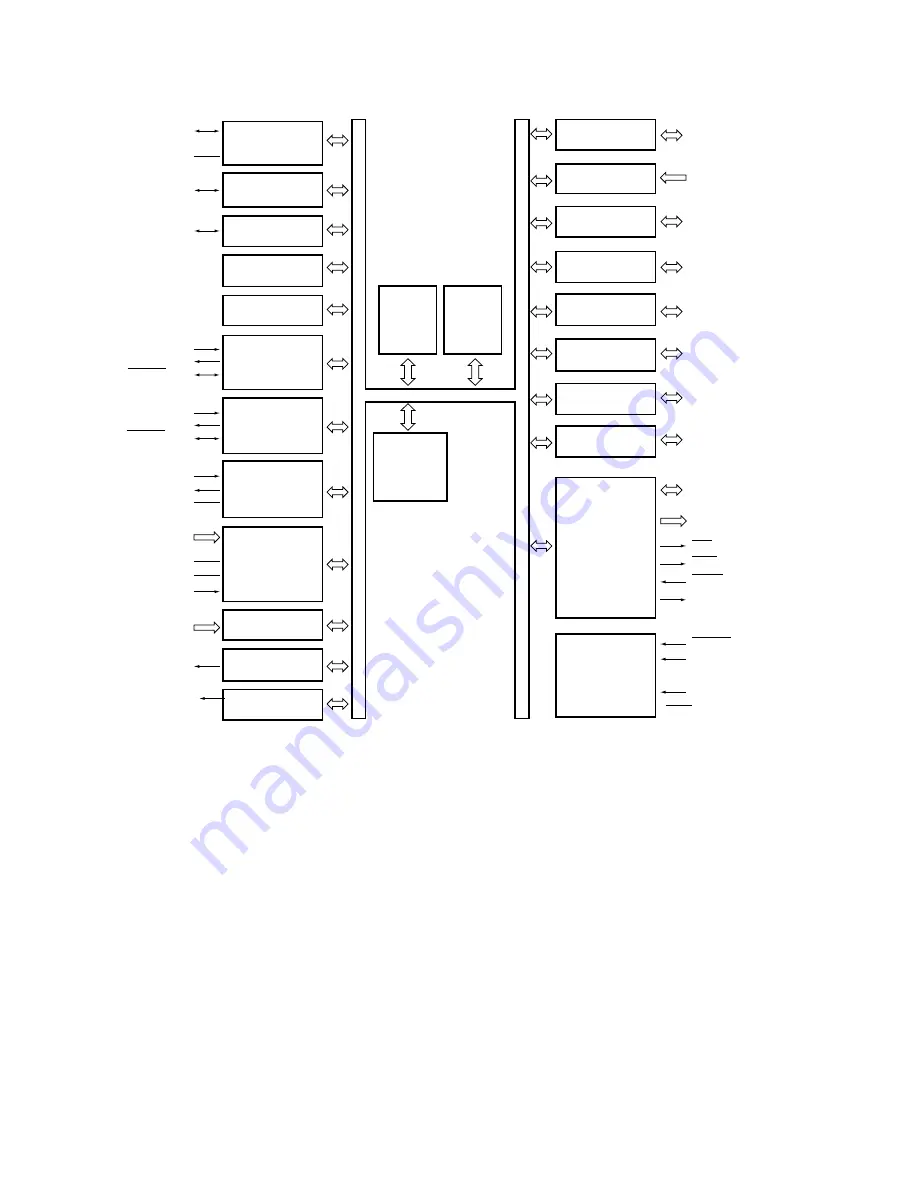

2. Block diagram

16bit Timer/

event counter

8bit Timer/

event counter 50

Watch timer

Watchdog timer

A/D

converter

Clock output

control

Buzzer output

78K/0

CPU core

ROM

32k Bytes

RAM

1024 Bytes

Port 0

Port 1

Port 2

Port 3

Port 4

Port 5

Port 6

Port 7

System control

AD0/P40 to AD7/P47

A8P50 to A15/P57

RD/P64

WR/P65

WAIT/P66

ASTB/P67

P00 to P03

P10 to P17

P20 to P25

P30 to P36

P40 to P47

P50 to P57

P64 to P67

P70 to P75

RESET

X1

X2

XT1

XT2

8bit Timer/

event counter 51

EXTERNAL

ACCESS

UART0

Serial

interface30

Serial

interface31

Interruput

control

V

DD0

V

DD1

Vss

0

Vss

1

IC

T100/TO0/P70

TI01/P71

RxD0/P23

TxD1/P24

ASCK0/P25

SI30/P20

SO30/P21

SCK30/P22

SI31/P34

SO31/P35

SCK31/P36

ANO0/P10 to ANI7/P17

AV

DD

AVss

AV

REF

INTP0/P00 to INTP3/P03

BUZ/P75

PCL/P74

TI50/TO50/P72

TI51/TO51/P73