RX-7001PGD

1-15

14

13

12

11

10

9

8

1

2

3

4

5

6

7

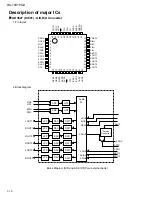

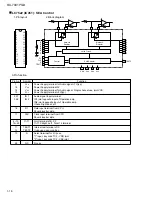

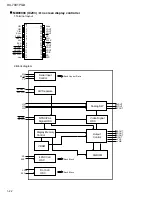

I/O 1

O/I 1

O/I 2

I/O 2

C2

C3

VSS

VDD

C1

C4

I/O 4

O/I 4

O/I 3

I/O 3

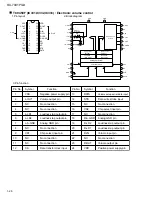

14

13

12

11

10

9

8

1

2

3

4

5

6

7

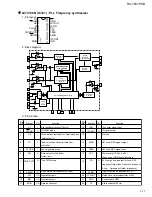

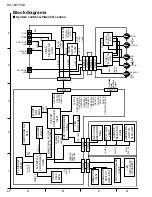

2.Block Diagram

1.Pin Layout

BU4066BCF (IC602,IC611) : Switch

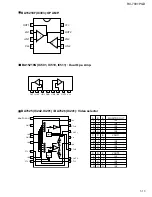

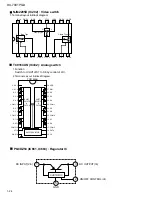

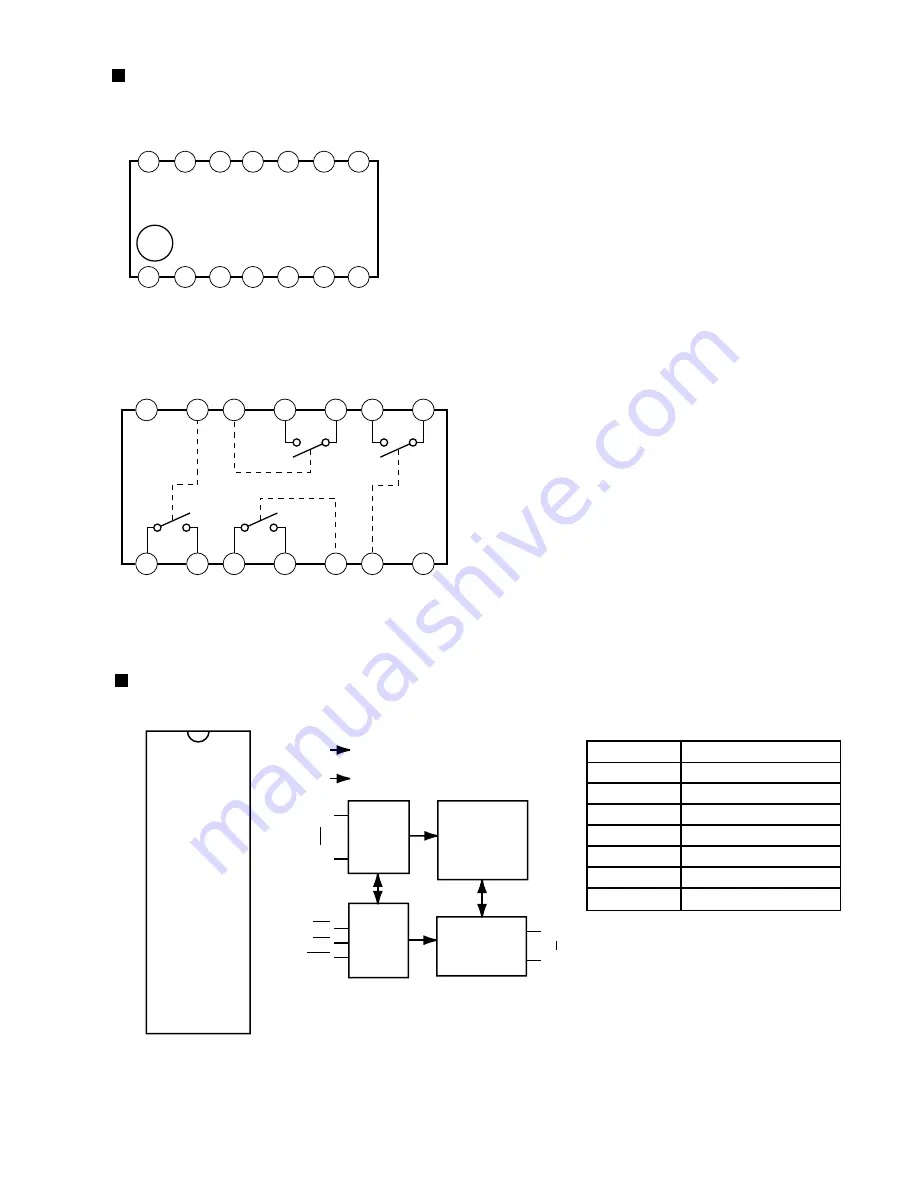

A0~A16

I/O1~I/O8

CS

WE

OE

Vdd

Vss

Address inputs

Data inputs/outputs

Chip select inputs

Write enable input

Output enable input

Power supply

Ground

Symbol

Description

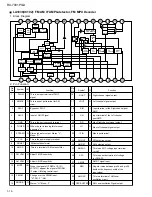

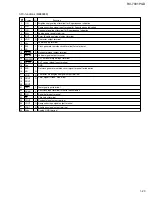

A0

A1

A2

A3

CS

I/O1

I/O2

VDD

VSS

I/O3

I/O4

WE

A4

A5

A6

A7

A16

A15

A14

A13

OE

I/O8

I/O7

VSS

VDD

I/O6

I/O5

A12

A11

A10

A9

A8

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

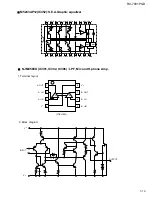

Vdd

Vss

A0

A16

CS

OE

WE

I/O1

I/O8

DECODER

CORE

ARRAY

CONTROL

DATA I/O

W24L011AJ-15(IC641):SDRAM

1.Pin layout

2.Block diagram

3.Pin function

Summary of Contents for RX-7001PGD

Page 28: ...2 1 ...

Page 47: ...RX 7001PGD 3 2 MEMO ...