TH-V70

1-26

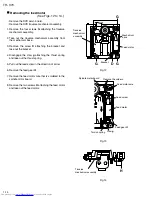

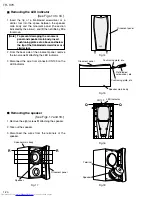

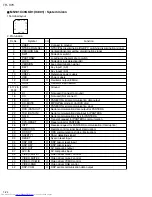

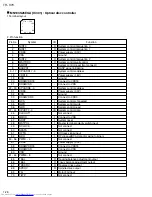

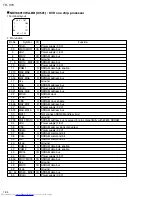

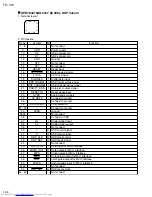

1. Terminal layout

MN102L62GLF1 (IC401) : Unit CPU

1

25

75

51

100 76

26 50

1

2

3

4

5

6

7

8

9

10

11

12

13 - 16

17

18

19

20

21

22

23

24

25

26 - 33

34

35 - 40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

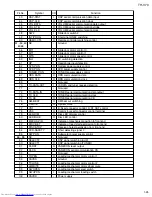

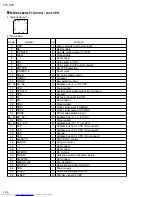

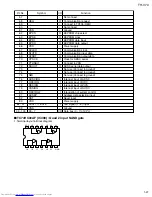

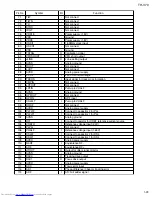

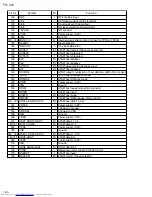

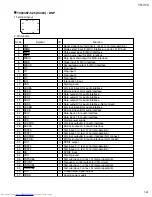

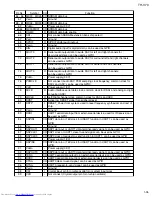

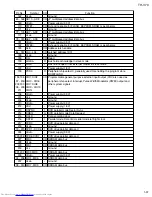

Pin No.

Symbol

Function

2. Pin function

I/O

WAIT

RE

/SPMUTE

WEN

-

CS1

CS2

HDTYPE

/DRVMUTE

SBRK

LSIRST

WORD

A0 - A3

VDD

SYSCLK

VSS

XI

XO

VDD

OSCI

OSCO

MODE

A4 - A11

VDD

A12 - A17

A18

A19

VSS

A20

DISCSTP

HAGUP

-

-

/HFMON

TRVSW

SWUPDN

MECHA_H/V

DISCSET

VDD

FEPEN

SLEEP

I

O

O

O

-

O

-

O

O

O

O

O

O

-

-

-

-

-

-

I

O

I

O

-

O

-

-

-

-

O

O

-

-

I

I

-

I

O

-

O

O

Micro computer wait signal input

Read enable

Spindle muting output to IC251

Write enable

Not connect

Chip select for ODC

Chip select for ZIVA (Not connect)

HD TYPE selection

Driver mute

SP motor brake control

LSI reset

Bus selection input

Address bus (0 - 3) for CPU

Power supply

System clock signal output (Not connect)

Ground

Not use (Connect to VSS)

Not connect

Power supply

Clock signal input (13.5MHz)

Clock signal output (13.5MHz)

CPU mode selection input

Address bus (4 - 11) for CPU

Power supply

Address bus (12 - 17) for CPU

Address bus 18 for CPU (Not connect)

Address bus 19 for CPU (Not connect)

Ground

Address bus 20 for CPU ( Not connect)

DISC STOP control

H/A gain control

Not connect

Not connect

HF monitor

Detection switch of traverse inside

Not connect

Disc detection

Serial enable signal for ADSC

Power supply

Serial enable signal for FEP

Standby signal for FEP

Summary of Contents for TH-V70

Page 55: ...TH V70 1 55 M E M O ...