TH-V70

1-41

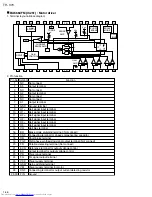

INSTRUCTION

REGISTER

INSTRUCTION

DECODE,

CONTROL

AND

CLOCK

GENERATION

ADD.

BUFFERS

DATA

REGISTER

16

R/W AMPS

AND

AUTO ERASE

16

DECODER

EEPROM

4096bit

256 x 16

VPP SW

VREF

VPP

GENERATOR

DO

DI

CS

SK

PE

1

2

3

4

PE

VCC

CS

SK

NC

GND

DO

DI

8

7

6

5

8 PIN SOP

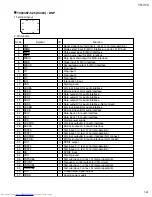

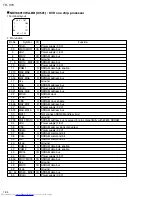

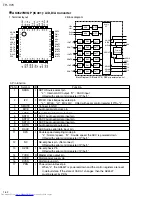

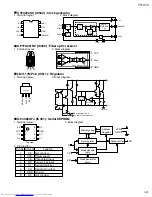

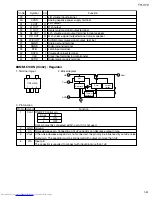

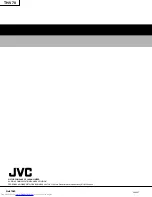

AK93C65AF (IC510) : EEPROM

1. Terminal layout

3. Block diagram

2. Pin function

NOTE : The pull-up resistor of the PE pin is about 2.5M (VCC=5V)

PE

VCC

CS

SK

DI

DO

GND

NC

1

2

3

4

5

6

7

8

Pin No. Symbol

Function

Not connect,

Program enable (With built-in pull-up resistor)

Power supply

Chip selection

Cereal clock input

Cereal data input

Cereal data output

Ground

Not connect

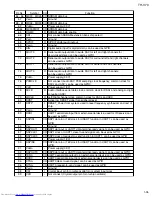

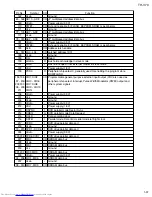

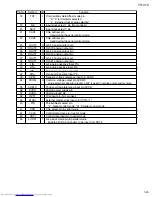

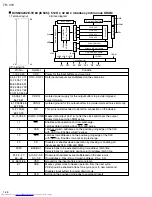

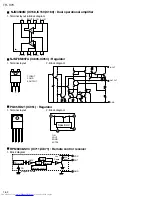

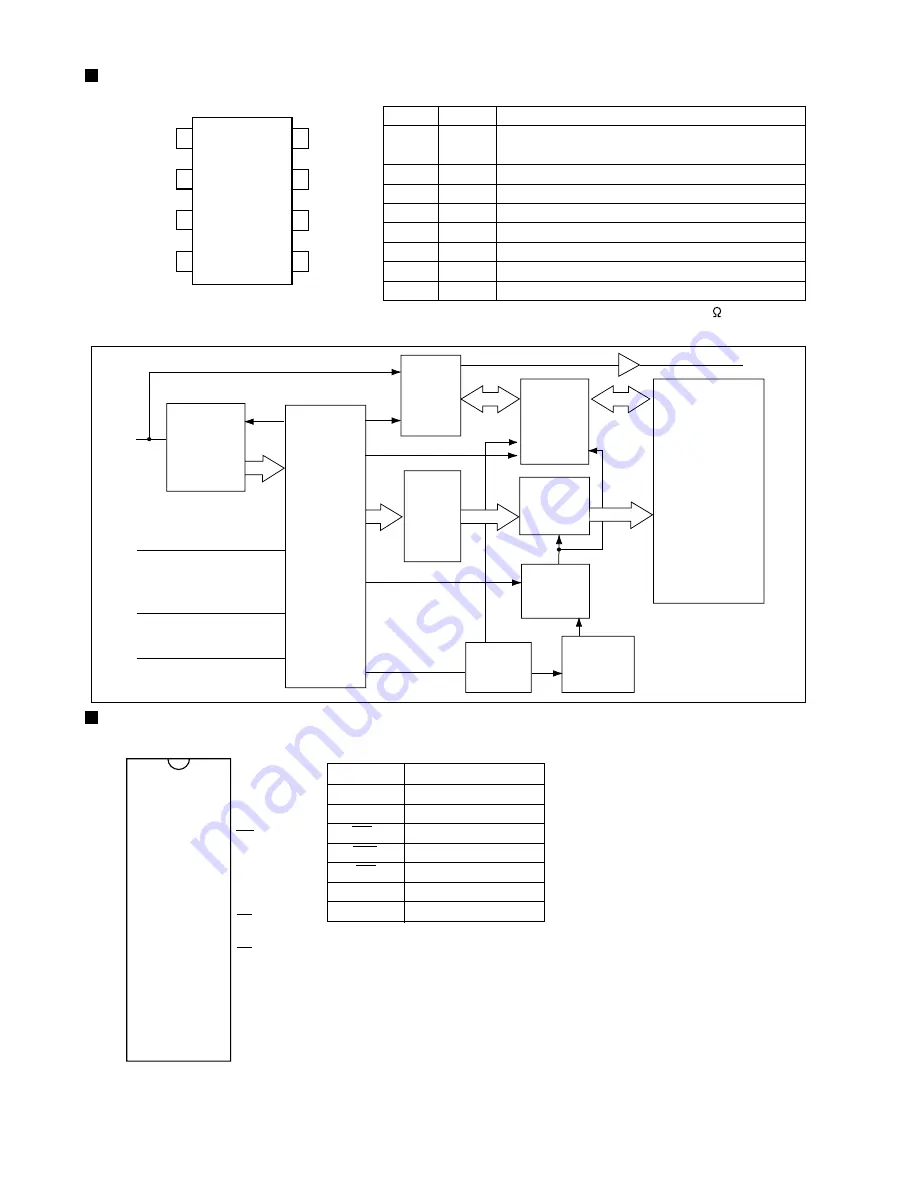

A0~A16

I/O1~I/O8

CS1

WE

OE

VDD

VSS

Address inputs

Data inputs/outputs

Chip select inputs

Write enable input

Output enable input

Power supply

Ground

Symbol

Function

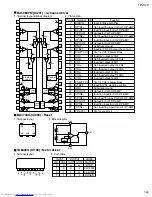

NC

A16

A14

A12

A7

A6

A5

A4

A3

A2

A1

A0

I/O1

I/O2

I/O3

VSS

VDD

A15

NC(CE2)

WE

A13

A8

A9

A11

OE

A10

CS1

I/O8

I/O7

I/O6

I/O5

I/O4

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

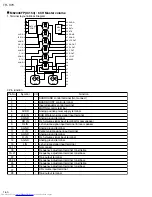

W24L010AJ-12/LP61L1024S-12-X (IC404) : SDRAM

1. Terminal layout

2. Pin function

Summary of Contents for TH-V70

Page 55: ...TH V70 1 55 M E M O ...