TH-V70

1-47

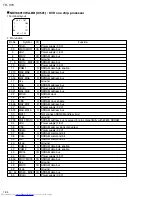

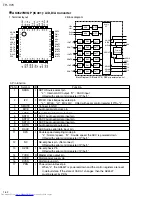

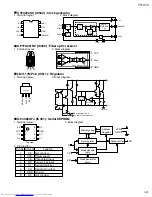

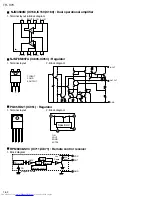

1. Terminal layout

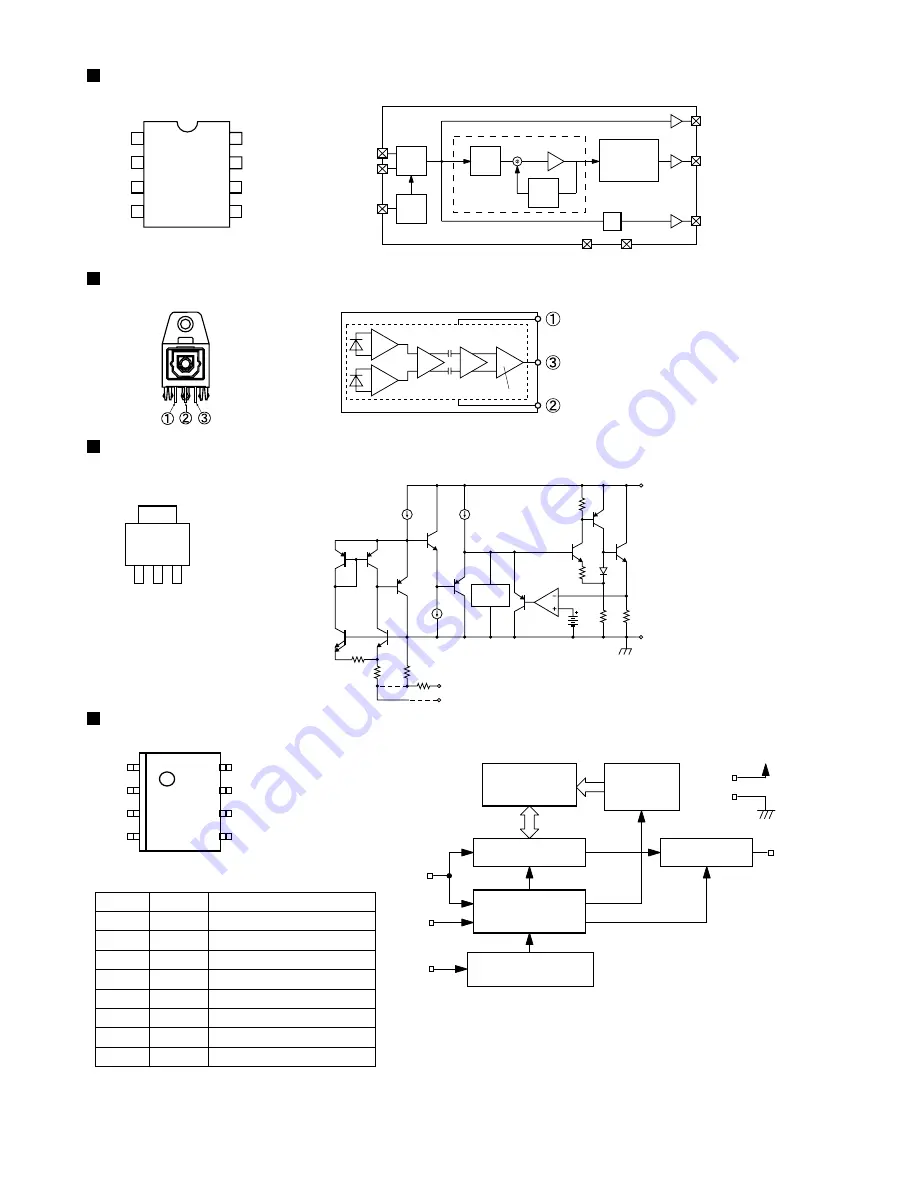

CY24203SC (IC502) : Clock generator

XOUT

27M

13.5M

16.9344M

8

7

6

5

XIN

VDD

VCXO

VSS

1

2

3

4

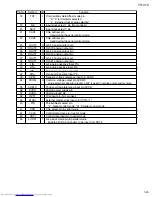

2. Block diagram

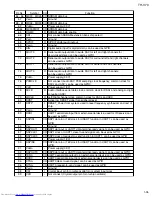

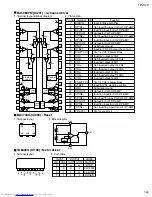

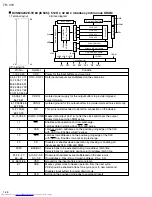

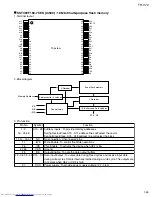

LM1117MP1.8 (IC511) : Regulator

1. Terminal layout

2. Block diagram

Top view

ADJ/GND

OUTPUT

INPUT

GND (FIXED OUTPUT)

ADJ.(ADJUSTABLE OUTPUT)

V

OUT

V

IN

Thermal

Limit

Current

Limit

Substrate

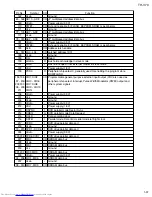

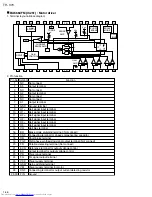

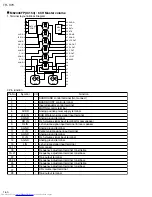

S-93C66AFJ (IC451) : Serial EEPROM

1. Terminal layout

3. Block diagram

PE

VCC

CS

SK

NC

GND

DO

DI

1

2

3

4

8

7

6

5

Top view

Memory array

Data register

Mode decode

logic

Clock generator

circuit

Output buffer

Address

decoder

VCC

GND

DO

DI

CS

SK

2. Pin function

PE

VCC

CS

SK

DI

DO

GND

NC

1

2

3

4

5

6

7

8

Pin No. Symbol

Function

Not connect

Power supply

Chip select input

Serial clock input

Serial data input

Serial data output

Ground

Not connect

OUTPUT

DIVIDERS

7 bit

/P

11bit

/Q

7 bit

PLL

16.9344M

27M

/2

13.5M

OSC

XIN

XOUT

ADC

8 bit

VCXO

VDD

VSS

VCO

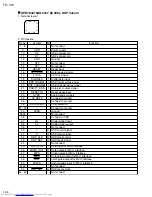

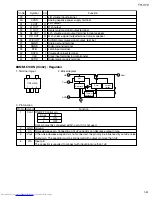

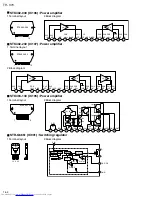

GP1FA351RZ (IC409) : Fiber optic receiver

1. Terminal layout

VCC

GND

Vout

2. Block diagram

AMP

AMP

AMP

AMP

Comp & Output circuit

Summary of Contents for TH-V70

Page 55: ...TH V70 1 55 M E M O ...