1-34

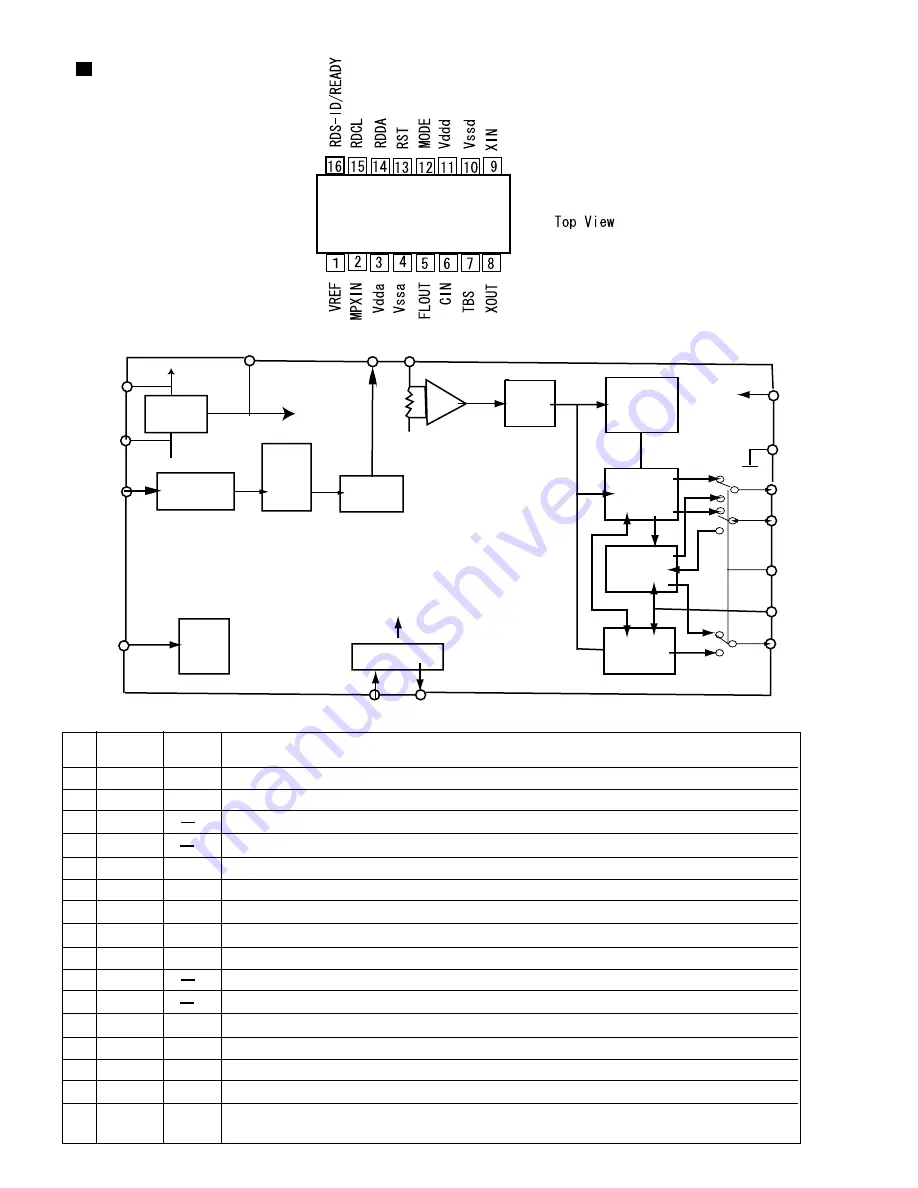

UX-V10GN

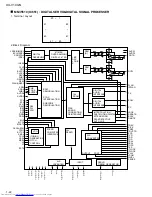

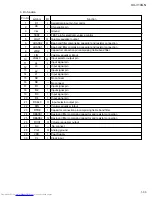

Pin Assignment

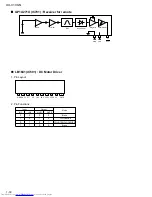

LC72723

Block diagram

Vdda

Vssa

MPXIN

TEST

TEST

VREF

FLOUT

CIN

Vddd

Vssd

RDDA

RDCL

MDDE

RST

RDS-ID/

READY

XDUT

XIN

REFERENCE

VOLTAGE

ANTIALIASING

FILTER

57kHz

BPF

(SCF)

VREF

SMOOTHING

FILTER

PLL

(57kHz)

CLOCK

RECOVERY

(1187.5kHz)

DATA

DECODER

RAM

(128-bits)

RDS-ID

DETECT

CLK(4.332MHz)

OSC

TEST

1.

2.

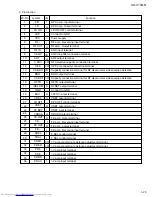

3. Pin functions

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Pin

No.

Symbol

Function

VREF

MPXIN

Vdda

Vssa

FLOUT

CIN

TEST

XOUT

XIN

Vssd

Vddd

MODE

RST

RDDA

RDCL

RDS-ID

READY

I/O

O

O

O

O

O

I

I

I

I

I

I

I/O

Reference voltage output (Vdda/2)

Baseband (multiplexed) signal input

Analog power supply (+5V)

Analog ground

Subcarrier input (comparator input)

Subcarrier input (filter output)

Test input

Crystal oscillator input (exeternal reference input)

Crystal oscillator output (4.332MHz)

Digtal ground

Digtal power supply

Read mode setting (0:master,1:slave)

RDS-ID/RAM reset (positive polarity)

RDS data output

RDS clock output (master mode)/RDS clock input (slave mode)

RDS-ID/READY output (negative polarity)

Summary of Contents for UX-V10GN

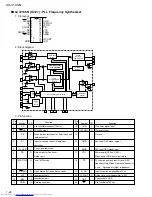

Page 32: ...1 32 UX V10GN LC75342 ...