XV-LTR1

1-27

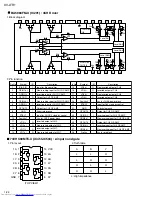

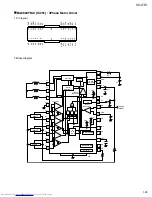

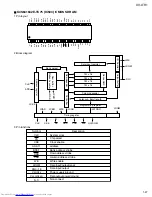

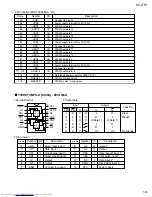

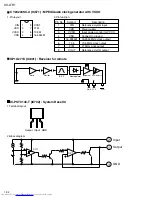

K4S641632E-TC75 (IC504) :CMOS SDRAM

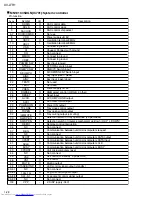

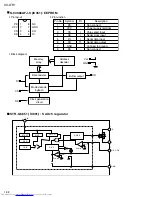

1.Pin layout

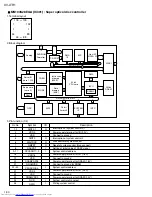

2.Block diagram

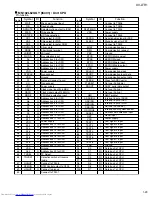

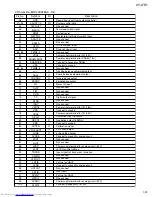

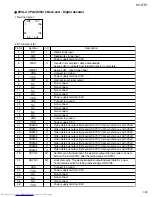

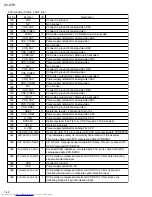

3.Pin functions

Bank select

Address register

Ro

w b

u

ff

er

Refresh counter

Ro

w decoder

Col.

b

u

ff

er

CLK

ADD

LCBR

LRAS

LCKE

LRAS

LCBR

LWE

LCAS

CLK

CKE

CS

RAS

CAS

WE

L(U)DQM

Timing register

LWCBR

LDQM

Programming register

Latency & Burst length

Column decoder

1M x 16

1M x 16

1M x 16

1M x 16

Data input register

Sense AMP

.

I/O Control

Output b

u

ff

er

LWE

LDQM

DQI

Vcc

DQ0

Vcc

Q

DQ1

DQ2

V

SSQ

DQ3

DQ4

Vcc

Q

DQ5

DQ6

V

SSQ

DQ7

Vcc

LDQM

WE

CAS

RAS

CS

BS0

BS1

A10/AP

A0

A1

A2

A3

Vcc

V

SS

DQ15

V

SSQ

DQ14

DQ13

Vcc

Q

DQ12

DQ11

V

SSQ

DQ10

DQ9

Vcc

Q

DQ8

V

SS

N.C

UDQM

CLK

CKE

NC

A11

A9

A8

A7

A6

A5

A4

V

SS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

Symbol

CLK

CS

CKE

A0~A11

BS0,1

RAS

CAS

WE

LDQM

DQ0~15

Vcc/Vss

Vccq/Vssq

N.C

System clock

Chip select

Clock enable

address

Bank address strobe

Row address strobe

column address strobe

Write enable

Data input/output mask

Data input/output

Power supply/ground

Data output power/ground

Non connect

Description