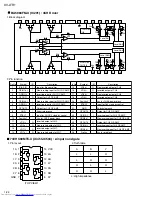

XV-LTR1

1-33

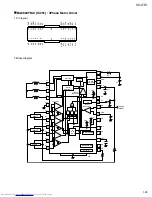

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171~173

174

175

176

-

-

I/O

I/O

I/O

I/O

I/O

-

-

I/O

I/O

I/O

I/O

I/O

-

-

I/O

-

I

I

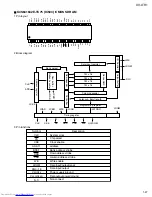

VSS

VDD3

HDD1

HDD13

HDD2

HDD12

HDD3

VDD3

VSS

HDD11

HDD4

HDD10

HDD5

HDD9

VDD3

VSS

HDD6~8

VDDH

NRESET

MASTER

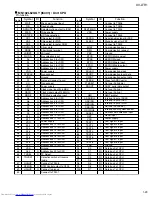

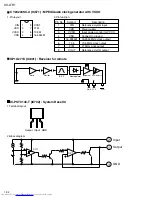

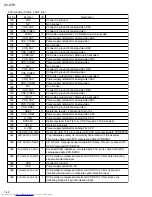

Pin No.

Symbol

I/O

Description

3.Pin function (MN103S28EGA : 4/4)

Connect to ground

Power supply terminal for I/O (3.3V)

ATAPI host data 1

ATAPI host data 13

ATAPI host data 2

ATAPI host data 12

ATAPI host data 3

Power supply terminal for I/O (3.3V)

Connect to ground

ATAPI host data 11

ATAPI host data 4

ATAPI host data 10

ATAPI host data 5

ATAPI host data 9

Power supply terminal for I/O (3.3V)

Connect to ground

ATAPI host data 6~8

Reference power supply for ATAPI (5.0V)

ATAPI host reset input

ATAPI master / slave select

1

2

3

4

5

6

7

CLR1

D1

CK1

PR1

Q1

Q1

GND

14

13

12

11

10

9

8

Vcc

CLR2

D2

CK2

PR2

Q2

Q2

CK1 D1

Q1 Q1

PR1CLR1

CK2

D2

Q2 Q2

PR2CLR2

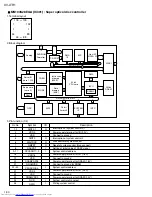

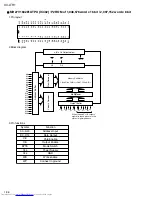

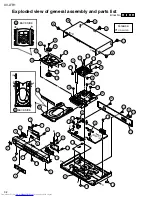

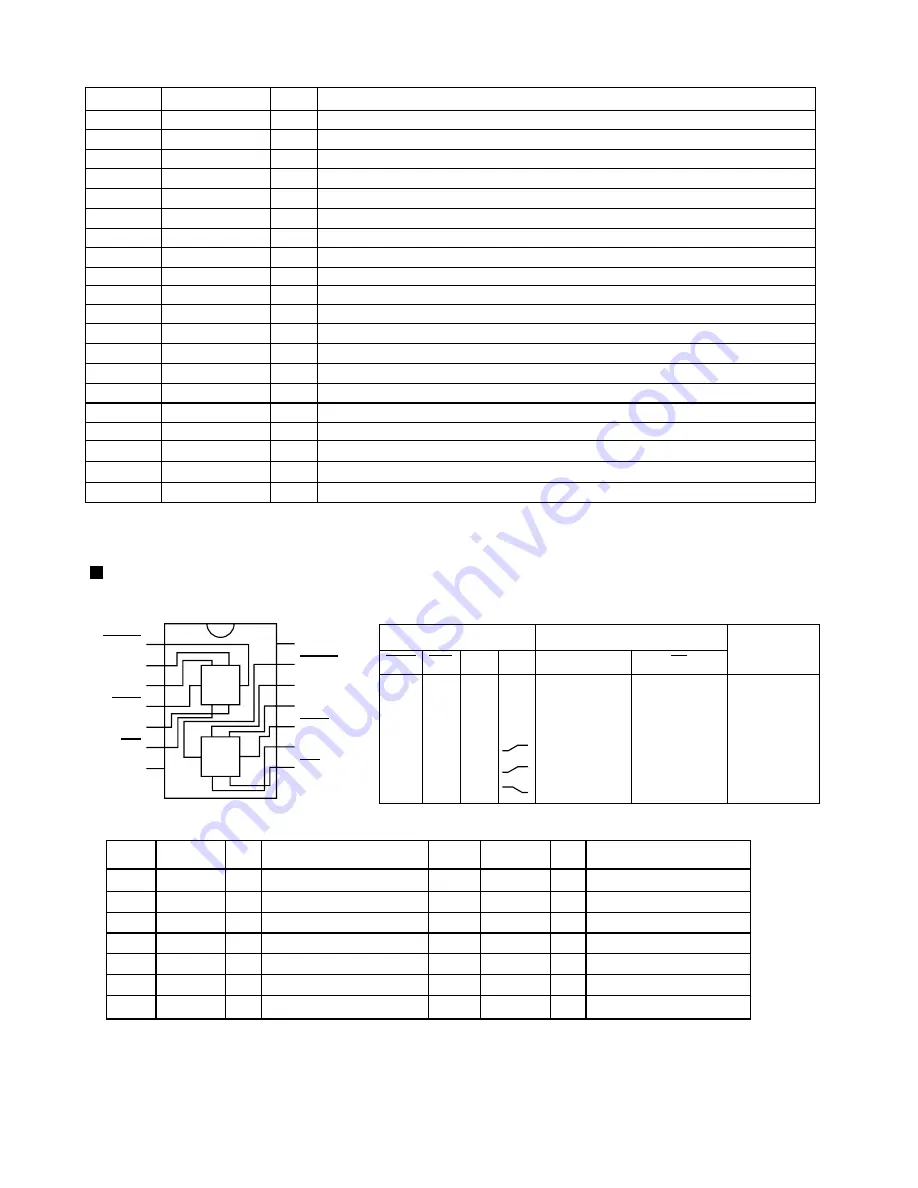

74VHC74MTC-X (IC454) : ZIVA Wait

1.Terminal layout

3.Pin function

2.Trouth table

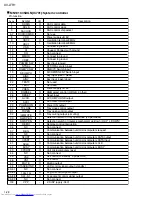

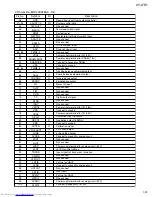

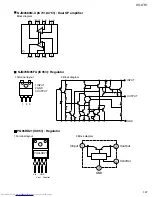

CLR

L

H

L

H

H

H

PR

H

L

L

H

H

H

D

X

X

X

L

H

X

CK

X

X

X

Q

L

H

H(Note 1)

L

H

Qn

Q

H

L

H(Note 1)

H

L

Qn

Input

Output

Function

Clear

Preset

No change

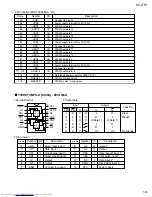

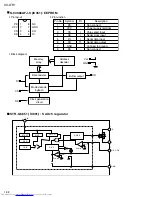

1

2

3

4

5

6

7

8

9

10

11

12

13

14

CLR1

D1

CK1

PR1

Q1

Q1

GND

Q2

Q2

PR2

CK2

D2

CLR2

VCC

Direct clear input 1

Data input 1

Clock pulse input 1

Direct preset input 1

Output

Output

Connect to ground

Output

Output

Direct preset input 2

Click pulse input 2

Data input 2

Clock clear input 2

Power supply

I

I

I

I

O

O

-

O

O

I

I

I

I

-

Pin No.

Symbol

I/O

Description

Pin No.

Symbol

I/O

Description