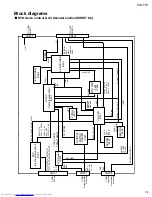

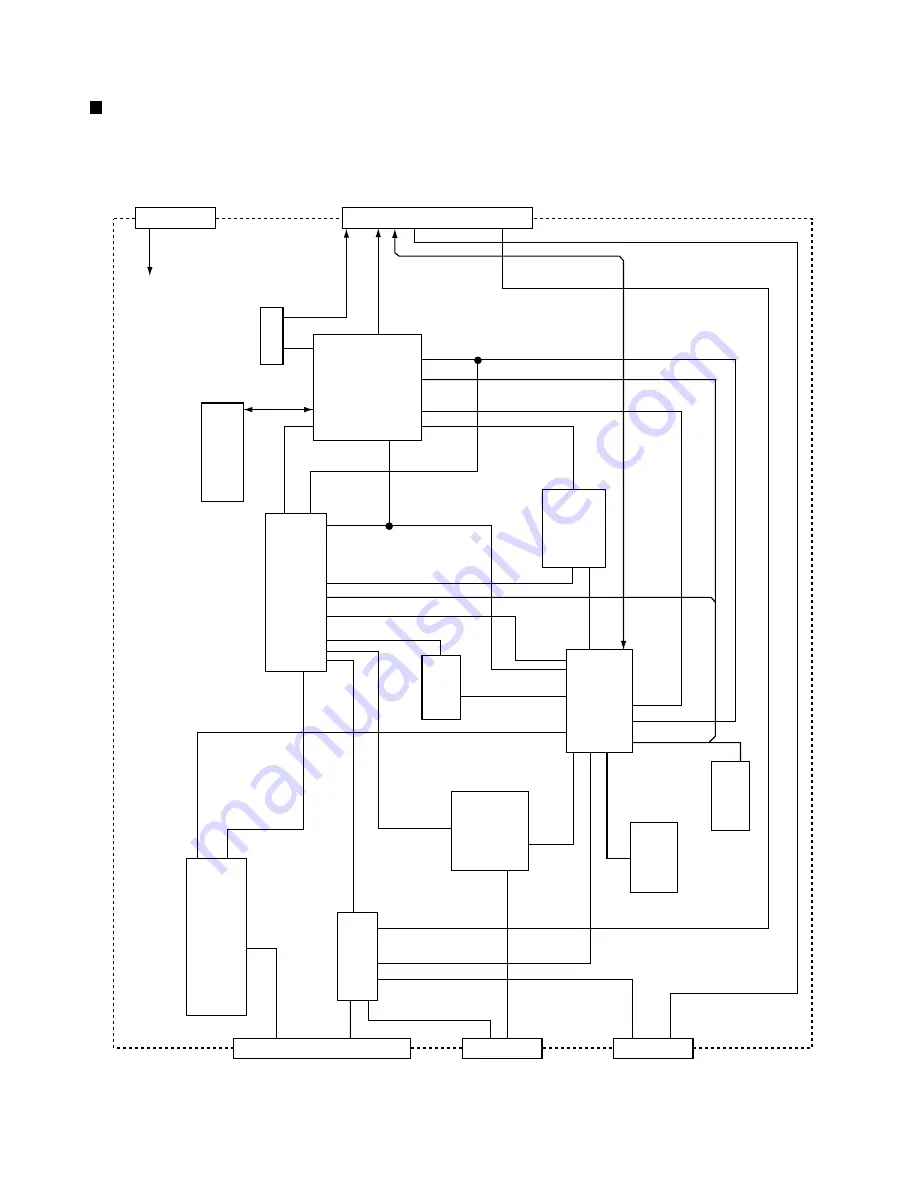

XV-LTR1

2-3

FEP

(F

ront end processor)

IC101

4CH Dr

iv

er

IC201

SPINDLE

M

OTO

R

DRIVER

IC251

SODC

(Optical disc controller)

IC301

ZIV

A W

AIT

Unit CPU

IC401

16M R

O

M

IC402

CN101

CN502

CN503

T1CD

T2CD F1CD F2CD

TR TC TD T

A

F2D

VD

F1D

VD

T+

T

-

F+ F-

TDOFS FODR

V

TRDR

V TRSDR

V

BDO OFTR

TBAL

TE RFENV

FBAL FE AS

ARF+ ARF-

TESTSG JLINE

FEPEN CPSCK SDOUT SLEEP

ADSCIRQ

ODCIRQ

ODCIRQ2

/WR /RD

/WR /RD

STD0~7

W

AIT

ODC

WAITDEC

W

AIT

DECIRQ

CPU

A0~20

CPUD0~7 CPU

A0~2

LSIRST

A

V

DECODER

IC501

27MHz

IC571

IC503

16M SDRAM

IC504

D

A-IEC

D

A_D

A

T

A

1

C/R/V

Y/B/U

CVBS/G/Y

CVBS

T

O

CN701

SHEET 4

T

O

CN961

SHEET 2

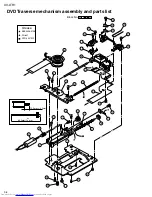

FR

OM

Pic

k-up

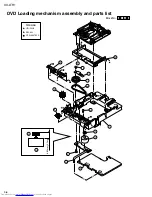

FR

OM

Spindle motor

assemb

ly

FR

OM

Loading

mechanism

assemb

ly

CPUD0~7

EPDO

EPDI

EPSK

EPCS

TX

IC454

IC455

CPUD0~7 CPU

A0~17

U2SDT S2UDT

SCLK

O REQ

B

USY CPURST

CN201

CN202

V+5V

Block diagrams

DVD Servo control & AV decoder section(SHEET 5,6)

FM+

FM-

LM+

LM-

VH

SM1~3

H1+~H3+

H1-~H3-

SBRK SPMUTE

FG SPDR

V

DRVMUTE

SW

OPEN SWUPDN

EPR

OM

IC451

OSCI/O

OSCI1

LMMUTE

TCLOSE

T

OPEN