Komodo II CoaXPress Frame Grabber Hardware and Installation Guide

20

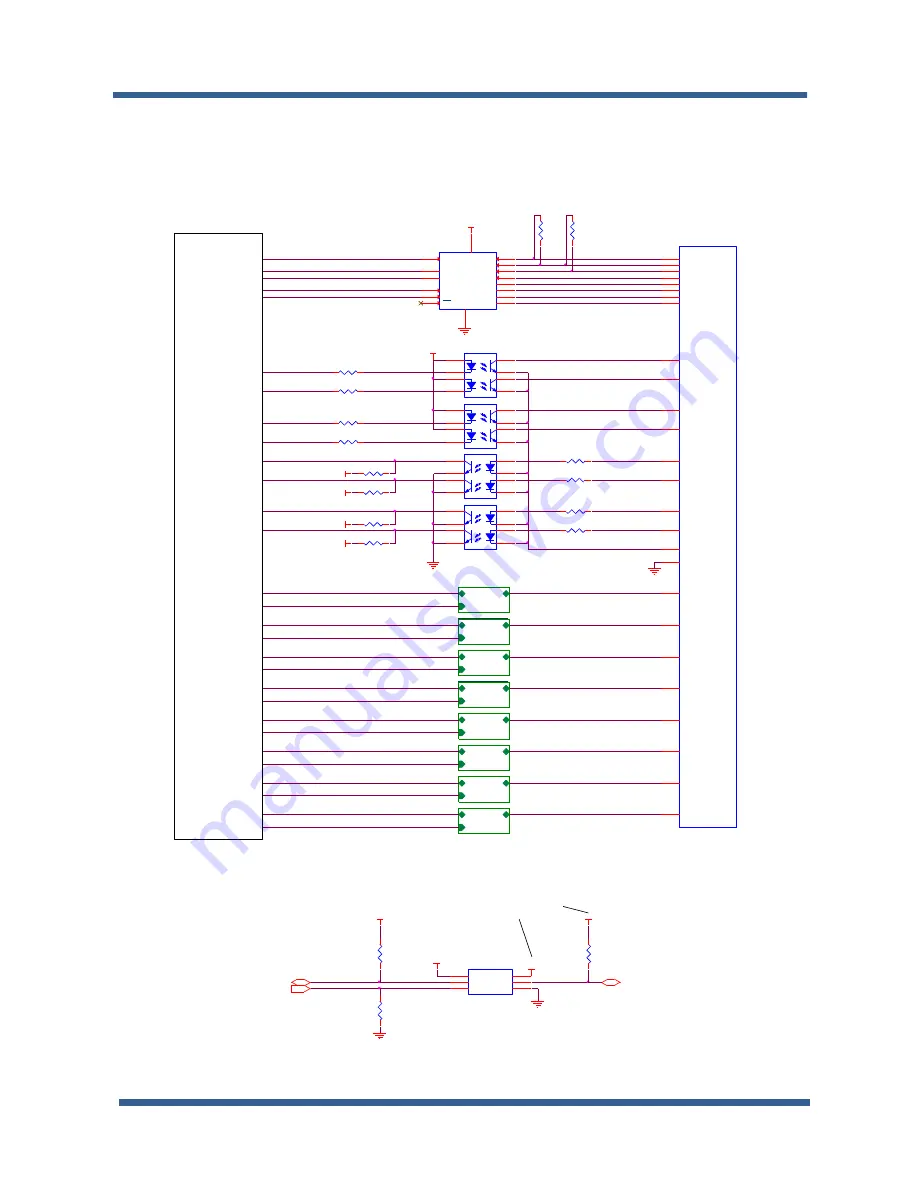

The electrical connection of the GPIO connectors is described following principal schematic

diagram:

Figure 8: GPIO Connectors schematic

Figure 9: Level shifters schematic

GPIO_OPTO_OUT2

GPIO_OPTO_OUT1

GPIO_OPTO_OUT0

GPIO_OPTO_OUT3

DS90LV049H

RIN1n

1

RIN1p

2

RIN2p

3

RIN2n

4

DOUT2n

5

DOUT2p

6

DOUT1p

7

DOUT1n

8

EN

9

DIN1

10

DIN2

11

VD

D

12

GN

D

13

ROUT2

14

ROUT1

15

EN

16

MOCD207M

1

8

2

3

4

6

5

7

MOCD207M

1

8

2

3

4

6

5

7

GPIOE_OPTO_OUT0

GPIOE_OPTO_OUT2

GPIOE_OPTO_OUT1

GPIOE_OPTO_OUT3

GPIOE_LVDS_IN1n

GPIOE_LVDS_OUT1p

GPIOE_LVDS_OUT1n

MOCD207M

1

8

2

3

4

6

5

7

GPIOE_LVDS_OUT0p

GPIOE_LVDS_OUT0n

MOCD207M

1

8

2

3

4

6

5

7

GPIO_LVDS_IN1

GPIO_LVDS_IN0

GPIO_LVDS_OUT0

GPIO_LVDS_OUT1

GPIOE_OPTO_IN2

GPIOE_OPTO_IN1

GPIOE_OPTO_IN0

GPIOE_OPTO_IN3

GPIO_OPTO_IN1

GPIO_OPTO_IN0

GPIO_OPTO_IN3

GPIO_OPTO_IN2

GPIO_LVDS_EN

1k

1k

1k

1k

91

91

91

91

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

LEVEL_SHIFTER0

B

A

DIR

GPIOE_TTL3

GPIOE_TTL2

GPIOE_TTL1

GPIOE_TTL0

LEVEL_SHIFTER3

B

A

DIR

LEVEL_SHIFTER2

B

A

DIR

LEVEL_SHIFTER1

B

A

DIR

GPIO_TTL1

GPIO_TTL0

GPIO_TTLDIR2

GPIO_TTLDIR1

GPIO_TTLDIR0

GPIO_TTL3

GPIO_TTL2

GPIO_TTLDIR3

100

100

LEVEL_SHIFTER4

B

A

DIR

LEVEL_SHIFTER5

B

A

DIR

LEVEL_SHIFTER6

B

A

DIR

LEVEL_SHIFTER7

B

A

DIR

GPIO_LVTTL0

GPIO_LVTTL3

GPIO_LVTTL2

GPIO_LVTTL1

GPIOE_LVTTL0

GPIOE_LVTTL1

GPIOE_LVTTL3

GPIOE_LVTTL2

GPIO_LVTTLDIR0

GPIO_LVTTLDIR1

GPIO_LVTTLDIR3

GPIO_LVTTLDIR2

3.3V

3V

1k

3V

1k

3V

1k

3V

1k

3V

GPIOE_LVDS_IN0n

GPIOE_LVDS_IN0p

GPIOE_LVDS_IN1p

FPGA

J7

B

A

DIR

74LVCH1T45

VCCA

1

A

3

GND

2

VCCB

6

B

4

DIR

5

10k

10k

10k

A

B

1.8V

DIR

5V / 3.3V

1.8V

5V / 3.3V

5V for TTL

3.3V for LVTTL

Installation and Configurations