Section 8

:

Status Model

Series 3700 System Switch/Multimeter Reference Manual

8-10

Document Number: 3700S-901-01 Rev. A / August 2007

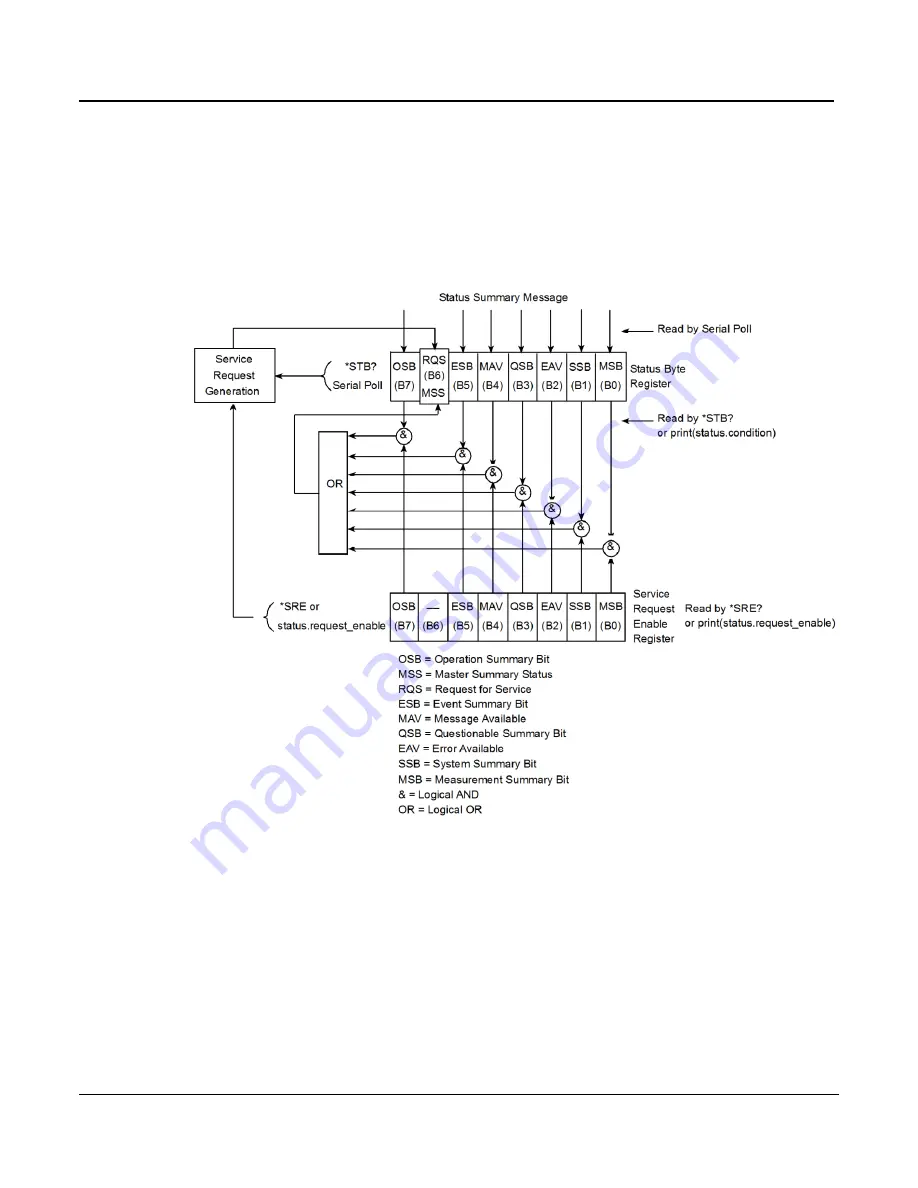

Status byte and service request (SRQ)

Service request is controlled by two 8-bit registers; the status byte register and the service

request enable register.

Figure 8-9: Status byte and service request (SRQ)

Status byte register

The summary messages from the status registers and queues are used to set or clear the

appropriate bits (B0, B1, B2, B3, B4, B5, and B7) of the status byte register. These summary

bits do not latch, and their states (0 or 1) are solely dependent on the summary messages (0 or

1). For example, if the standard event register is read, its register will clear. As a result, its

summary message will reset to 0, which in turn will reset the ESB bit in the status byte register.

The bits of the status byte register are described as follows: