DP-1100B II DP-1100B II

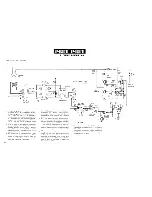

1 - 5 - 1 5 . D R O P O U T P O S I T I O N D E T E C T I O N O P E R A T I O N A N D P U F F , K I C F O P E R A T I O N

1. CIRCUIT DESCRIPTION

D e t e c t i o n of Dropout Position

1 . T h e d r o p o u t c o n t r o l c i r c u i t e m p l o y e d in t h i s u n i t has b e e n

d e s i g n e d t o be s t r o n g a g a i n s t s c r a t c h e s or s h o c k s . T h e

FGS signal ( 2 0 pulses g e n e r a t e d per o n e r e v o l u t i o n of t h e

disc m o t o r ) is a p p l i e d t o pin 3 9 (FGS) of IC15 ( T C 1 5 G or

T 7 0 0 1 ) a n d it is 6 t i m e s f r e q u e n c y m u l t i p l i e d internally.

A n o u t p u t w i t h 1 2 0 pulses per o n e r e v o l u t i o n is o u t p u t t o

pin 3 5 ( D O C K ) . If a s c r a t c h is p r e s e n t , the n u m b e r of

pulses are c o u n t e d . T h e level at pin 1 2 ( D C O N ) of IC15 is

s w i t c h e d f r o m " H " to " L " at t h e s a m e p o s i t i o n w h e r e t h e

s c r a t c h w a s p r e s e n t b u t o n e t r a c k b e h i n d . Q 8 a n d Q 9 in

t h e t r a c k i n g s e r v o c i r c u i t are t u r n e d O N to increase t h e

g a i n of t h e t r a c k i n g s e r v o c o n t r o l . T h u s , t h e s y s t e m is p r o

t e c t e d a g a i n s t s c r a t c h e s or s h o c k s .

2 . If a s c r a t c h is f o u n d o n t h e s u r f a c e of a d i s c , pin 8 (RFES)

of c o m p a r a t o r I C 1 0 ( 2 / 2 ) is s w i t c h e d f r o m " L " level t o

" H " level a n d pin 2 2 of I C 1 5 t u r n s t o " H " level. W h e n

pin 2 2 b e c o m e s " H " l e v e l , a shift register is set inside

I C 1 5 a n d t h e DOCK signal ( 1 2 0 pulses per o n e r e v o l u t i o n

o f disc) is c o u n t e d . Both of t h e shift register inside IC15

a n d e x t e r n a l register IC9 are u s e d for t h e c o u n t i n g pur

p o s e . W h e n t h e 1 2 0 pulses are c o u n t e d , t h e o u t p u t is

available at pin 5

(D

OU

T)

of IC9 a n d it is f e d t o pin 11 of

IC7. Its o u t p u t is o b t a i n e d f r o m pin 8 a n d it is f e d t o pin 3 4

(DIN) of I C 1 5 . T h i s c h a n g e s t h e level at pin 1 2 ( D C O N )

f r o m " H " t o " L " .

F I G . 1 - 5 - 1 5

3. T r a c k i n g error pulse c o n t r o l signal is p r e s e n t at pin 1 (TEP)

of IC15 a n d it is " H " level d u r i n g t h e n o r m a l PLAY m o d e .

It, h o w e v e r , s w i t c h e s t o " L " level d u r i n g KICK m o d e . This

is i n p u t t o pin 3 a n d 1 2 of IC9 t o disable t h e c i r c u i t d u r i n g

t h a t m o d e .

RF waveform

DCON signal

Dropout position detection

(used a s 1 1 4 bit shift register)

5 3

When a scratch is present on disc

Summary of Contents for DP-1100 B

Page 3: ...D P 1 1 0 0 B II D P 1 1 0 0 B II I BLOCK DIAGRAM ...

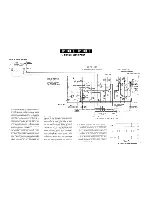

Page 32: ...D P 1 1 0 0 B II 1 CIRCUIT DESCRIPTION Disc Scratch Dust RFES D C O N D O C K Fig 1 2A 3 5 ...

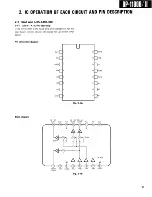

Page 112: ...2 IC OPERATION OF EACH CIRCUIT AND D P 1 1 0 0 B II PIN DESCRIPTION Fig 2 4 1 G 1 ...

Page 117: ...DP 1100B II I OPERATION OF MAIN MICROPROCESSOR Fig 3 1D Q data reading flow chart ...