DV-6050

7

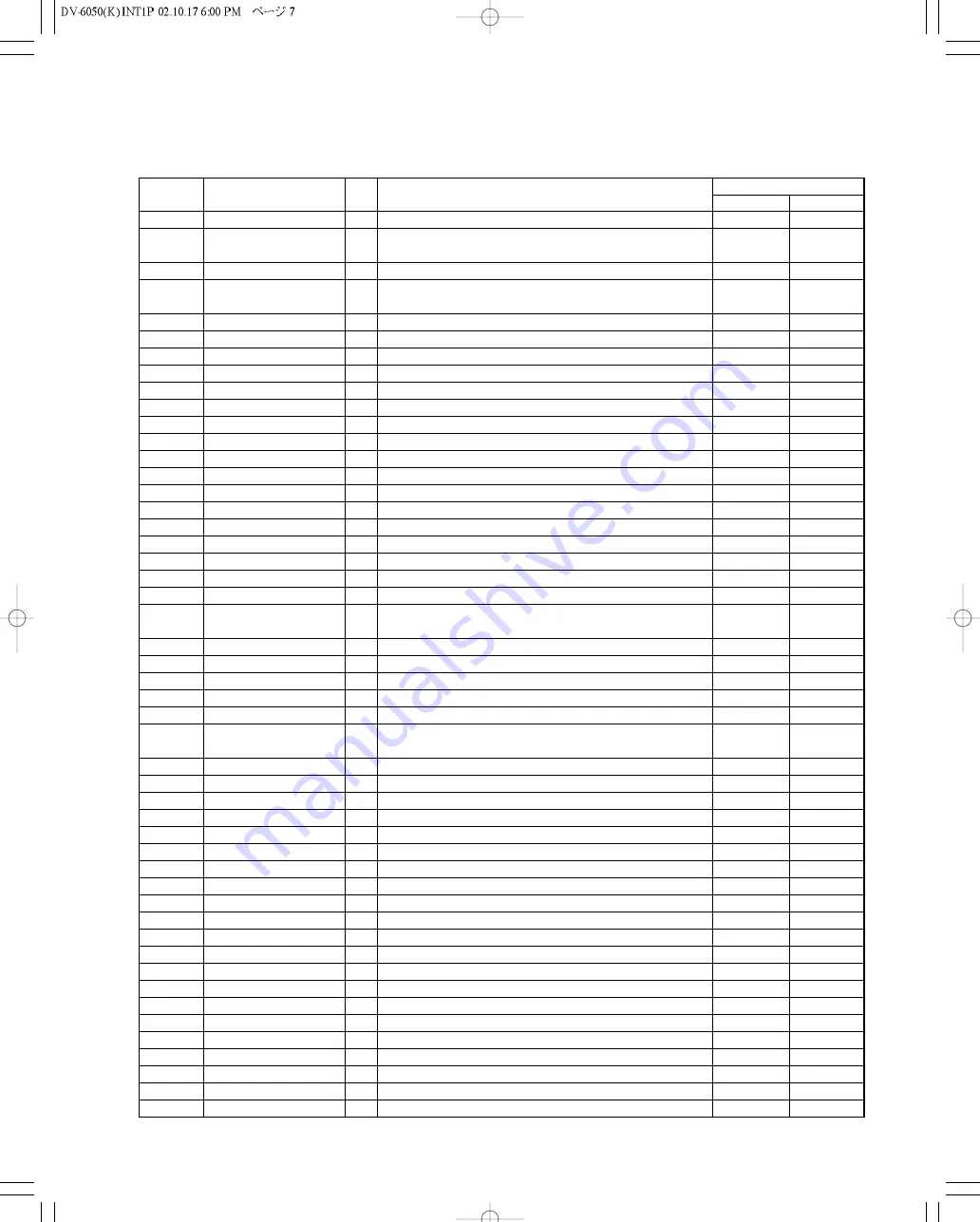

CIRCUIT DESCRIPTION

Pin No.

Pin Name

I/O

Pin Description

Logic

H

L

1

WAIT

I

Bus wait port.

2

NRD(ODC/AVDEC

O

Bus read port for ODC/AV Decoder/SRAM.

/SRAM)

3

NWEL

O

Bus read port for AV Decoder/RAM.

4

NWEH(ODC/AVDEC

O

Bus read port for ODC/AV Decoder/SRAM/ROM.

/SRAM/ROM)

5

RAMCS(SRAM)

O

SRAM chip select.

6

ODCCS

O

ODC chip select.

7

AVCS(AVDEC)

O

AV decoder chip select.

8

ROMCS(ROM)

O

Flash ROM chip select.

9

SCLOCK(VDAC)

I/O VDAC 12C clock.

10

SDATA(VDAC)

I/O VDAC 12C data.

11

FRD(ROM)

O

Flash ROM read port.

12

WORD

I

CSO bus width.

13~16

CPUADR(0~3)

O

Bus address (0~3).

17

VDD

-

Supply voltage (+3.3V).

18

SYSCLK(AVDEC)

O

External clock output for AV decoder.

19

VSS

-

Connected to ground.

20

XI

I

Unused.

21

XO

O

Unused.

22

VDD

-

Supply voltage (+3.3V).

23

OSCI(CLK135)

I

System clock input (13.5MHz).

24

OSCO

O

Unused.

25

MODE

I

Processor mode selection.

Expension

Mode

26~33

CPUADR4~11

O

Bus address (4~11).

34

AVDD

-

Supply voltage (+3.3V).

35~42

CPUADR12~19

O

Bus address (12~19).

43

VSS

-

Connected to ground.

44

CPUADR20

O

Bus address (20).

45

CDH

O

Switching of DAC.

CD

Except

CD

46

HFMON

O

HF monitor output of ADSC.

47

25BSY

O

Writing busy data output.

Normal

Busy

48

KMODE

I

Selection of writing mode for the ROM.

Writing

Normal

49

196BSY

I

Busy data input.

Normal

Busy

50

FROMWR

O

Enable control for writing jig.

51

TRVSW

I

Input port of traverse switch.

Off

On

52

AMUTE

O

Audio mute control.

53

FEPRST

O

FEP reset output.

54

VDD

-

Supply voltage (+3.3V).

55

FEPEN

O

Enable output to FEP (traverse).

56

NC

O

Unused.

57

STBSACD

O

Unused.

58

STBSP1

O

Strobe output to serial-parallel converter.

59

STBDAC1

O

Strobe output to ADAC.

60

STBPSL

O

Strobe output.

61

VSS

-

Connected to GND.

62

MSREADY

I

SACD ready signal input.

63

E2CS

O

Chip select to EEPROM.

64

PROGSW

I

Input port of program switch.

Progressive

Interlace

65

ICRST

O

Reset signal output to periphery ICs.

66

VDD

-

Supply voltage (+3.3V).

1-2 Pin Description of DVD Microcomputer : MN102LP62G (DVD AUDIO FRONT END, IC26)