KDC-CX85/CPS85

6

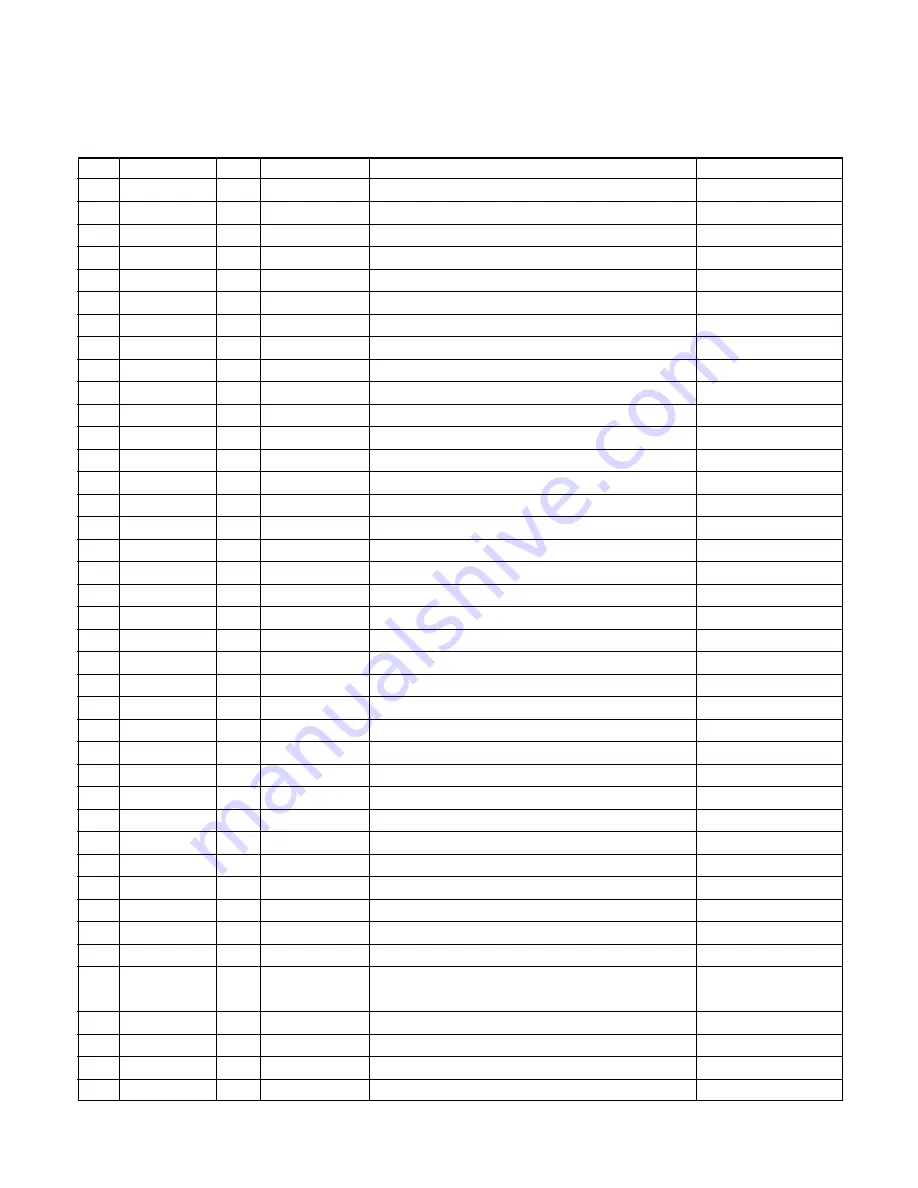

MICROCOMPUTER’S TERMINAL DESCRIPTION

Pin

Pin Name

I/O

Function

Description

Processing Operation

41

P21/TxD1/SO1

O

DATAC

Data output from the changer

42

P22/ASCK1/SCK1

I/O

HCLK

Communication clock input from H/U

43

P23/PCL

O

REQC

Communication request to H/U

44

P24/BUZ

O

CHMUTE

Audio mute output to H/U

L: Mute ON

45

P25/SI0/SDA0

I

TXTDATA

Text data input

46

P26/SO0

O

Not used.

47

P27/SCK0/SCL0

O

TXTCLK

Text clock output

48

P80/A0

O

A0

Address setting terminal for S-RAM

49

P81/A1

O

A1

Address setting terminal for S-RAM

50

P82/A2

O

A2

Address setting terminal for S-RAM

51

P83/A3

O

A3

Address setting terminal for S-RAM

52

P84/A4

O

A4

Address setting terminal for S-RAM

53

P85/A5

O

A5

Address setting terminal for S-RAM

54

P86/A6

O

A6

Address setting terminal for S-RAM

55

P87/A7

O

A7

Address setting terminal for S-RAM

56

P40/AD0

I/O

D0

Data input/output terminal with S-RAM

57

P41/AD1

I/O

D1

Data input/output terminal with S-RAM

58

P42/AD2

I/O

D2

Data input/output terminal with S-RAM

59

P43/AD3

I/O

D3

Data input/output terminal with S-RAM

60

P44/AD4

I/O

D4

Data input/output terminal with S-RAM

61

P45/AD5

I/O

D5

Data input/output terminal with S-RAM

62

P46/AD6

I/O

D6

Data input/output terminal with S-RAM

63

P47/AD7

I/O

D7

Data input/output terminal with S-RAM

64

P50/A8

O

A8

Address setting terminal for S-RAM

65

P51/A9

O

A9

Address setting terminal for S-RAM

66

P52/A10

O

A10

Address setting terminal for S-RAM

67

P53/A11

O

A11

Address setting terminal for S-RAM

68

P54/A12

O

A12

Address setting terminal for S-RAM

69

P55/A13

O

A13

Address setting terminal for S-RAM

70

P56/A14

O

A14

Address setting terminal for S-RAM

71

P57/A15

O

A15

Address setting terminal for S-RAM

72

VSS

-

VSS

Ground potential connection terminal

73

P60/A16

O

A16

Enable control terminal for S-RAM

74

P61/A17

O

A17

Enable control terminal for S-RAM

75

P62/A18

O

RAMOK

RAM check judging terminal for production

76

P63/A19

I

ELVADJ

Mechanism deck ascent/descent position

L: Adjustment mode

adjustment mode

77

P64/RD

O

RD

Read-out to S-RAM control output

78

P65/WR

O

WR

Write to S-RAM control output

79

P66/WAIT

I

WAIT

Insertion of weight when accessing S-RAM

80

P67/ASTB

O

ASTB

Chip selection to S-RAM