NXR-800H

15

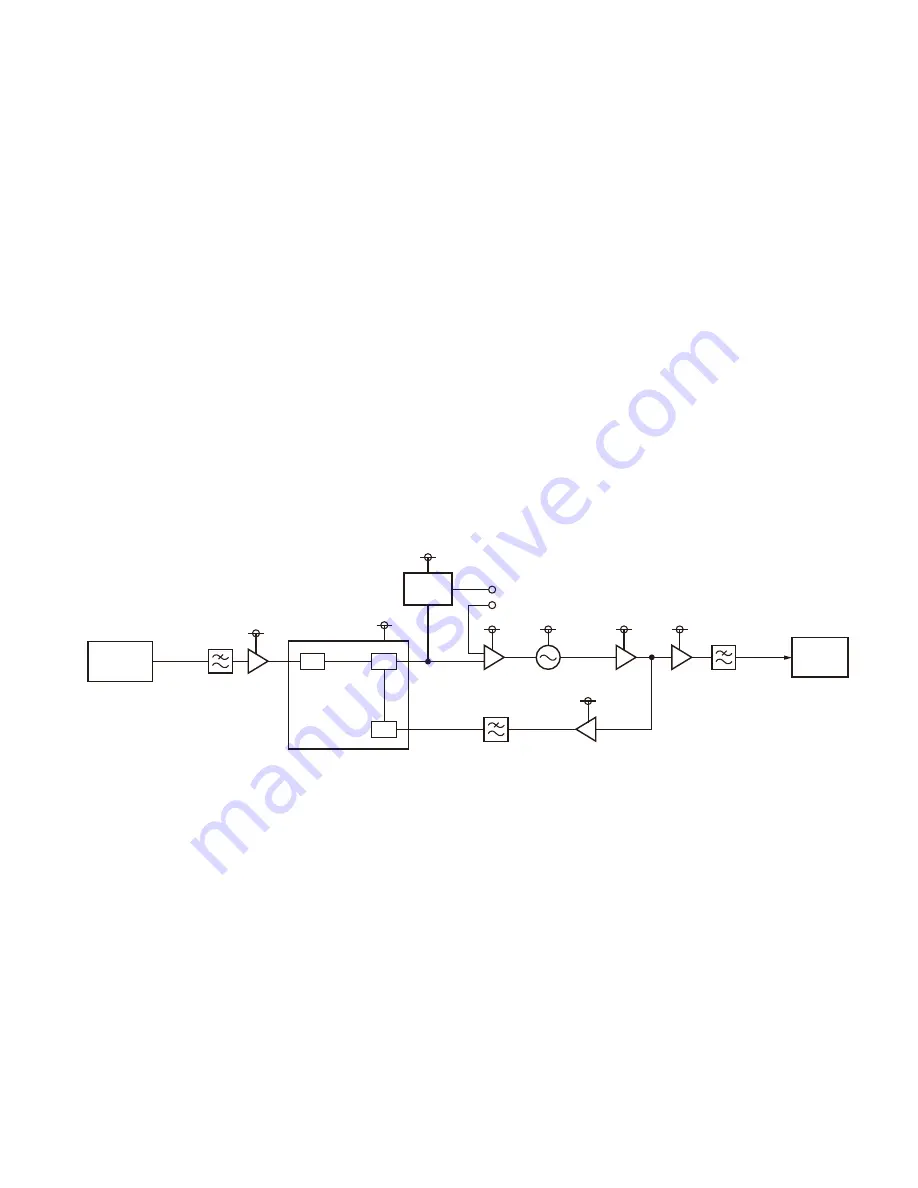

2-3. Transmitter modulation 19.2MHz PLL circuit

The transmitter modulation 19.2MHz PLL circuit produces

the reference frequency signal for the Transmitter DDS cir-

cuit and modulates the low-frequency components.

The circuit consists of IC302, IC303, IC305, X301, Q304,

Q305, and Q307.

The signal generated by the VCXO (X301) is fed to the

buffer amplifi er Q307.

The VCXO (X301) signal enters buffer amplifi er Q307 and

is amplifi ed by Q305. The higher harmonic wave is attenu-

ated by the LPF and returns to IC303. Its phase is com-

pared with that of the reference frequency 5kHz.

The phase difference signal produced by the comparing

phase is converted to a DC voltage by a lag-lead type loop

fi lter. This DC voltage is input to the IC305 invert amplifi er

(B/2) and is synthesized with the modulating signal. This

DC voltage is input to the X301 control voltage terminal for

controlling the VCXO oscillating frequency 19.2MHz.

The DC voltage passes through the IC306 operational am-

plifi er, and is output as a voltage signal (CVT-MOD) for moni-

toring the modulating 19.2MHz PLL circuit lock voltage.

The 19.2MHz oscillating signal is fed to the Q307 buffer

amplifier and is amplified by Q304. The higher harmonic

wave is attenuated by the LPF, fed to IC307, and is used as

the reference frequency signal of the transmitter DDS cir-

cuit.

Q305

TX Ref

19.2MHz

PLL circuit

1/R

1/N

PD

Fref.=19.2MHz

R=3840

Fpd=5kHz

8V #2

Q307

X301

IC302

5V #2

IC305

5V #2

8V #2

8V #2

8V #2

5V #2

19.2MHz

IC306

OP-AMP

Q304

5V #2

2

8

6

19.2MHz

IC303

PLL IC

CVT-MOD

TX DDS

circuit

19.2MHz

Mod signal

Fig. 3 Transmitter modulation 19.2MHz PLL circuit /

图 3 发射机调制 19.2MHz PLL 电路

2-4. Transmitter DDS circuit

The transmitter DDS circuit produces the transmitter

main PLL reference frequency signal 4.5MHz.

This circuit consists of IC307, IC202, CF201, Q210, Q211,

Q212 and Q213.

The 19.2MHz signal from the transmitter modulation

19.2MHz PLL circuit is amplifi ed by IC307 and supplied to

the IC202 reference signal pin.

IC202 produces the transmitter main PLL 4.5MHz refer-

ence frequency signal based on 19.2MHz on signal.

The spurious output by IC202 is attenuated by CF201

and LPF, 4.5MHz reference frequency signal is amplified

by Q211, Q212, and Q213, and fed to the transmitter main

PLL.

The comparison frequency of the transmitter main PLL is

100kHz and the PLL frequency step is 100kHz.

However, minute frequency step such as 2.5kHz and

3.125kHz because the DDS output frequency is variable.

CIRCUIT DESCRIPTION /

电路说明

2-3. 发射机调制 19.2MHz PLL 电路

发射机调制 19.2MHz PLL 电路产生发射机 DDS 电路的基准

频率信号,并调制低频分量。

该 电 路 由 I C302、I C303、I C305、X301、Q304、Q305 和

Q307 组成。

VCXO(X301) 生成的信号被送入缓冲放大器 Q307。

V C X O ( X301) 信号进入缓冲放大器 Q307,由 Q305 放大。较

高的谐波由 L P F 衰减并返回 I C303。其相位与基准频率 5k H z

的相位进行对比。

通过相位对比产生的相位差信号由一个滞后超前式环路滤

波器转换为 DC 电压。该 DC 电压被输入 IC305 反相放大器 (B/2)

并与调制信号合成。该 D C 电压被输入用于控制 V C X O 振荡频

率 19.2MHz 的 X301 控制电压端子。

DC 电压通过 IC306 运算放大器,

输出为电压信号 (CVT-MOD),

用于监测调制 19.2MHz PLL 电路锁定电压。

19.2M H z 振荡信号被送入 Q307 缓冲放大器,由 Q304 放大。

较高的谐波由 LPF 衰减,送入 IC307,用作发射机 DDS 电路的

基准频率信号。

2-4. 发射机 DDS 电路

发射机 DDS 电路产生发射机主 PLL 基准频率信号 4.5MHz。

该 电 路 由 I C307、I C202、C F201、Q210、Q211、Q212 和

Q213 组成。

来 自 发 射 机 调 制 19.2M H z P L L 电 路 的 19.2M H z 信 号 由

IC307 放大并提供给 IC202 基准信号针脚。

IC202 产生基于信号上的 19.2MHz 的 PLL 4.5MHz 基准频率

信号。

I C202 的寄生输出由 C F201 和 L P F 衰减,4.5M H z 基准频率

信号由 Q211、Q212 和 Q213 放大,并被送入发射机主 PLL。

发 射 机 主 P L L 的 比 较 频 率 为 100k H z,P L L 频 率 步 长 为

100kHz。

但是,微小频率步长为 2.5k H z 和 3.125k H z,因为 D D S 输

出频率是可变的。

Summary of Contents for NXR-800H

Page 180: ...1 E CN300 RX_IF_VN 168 ...