TK-2107G

11

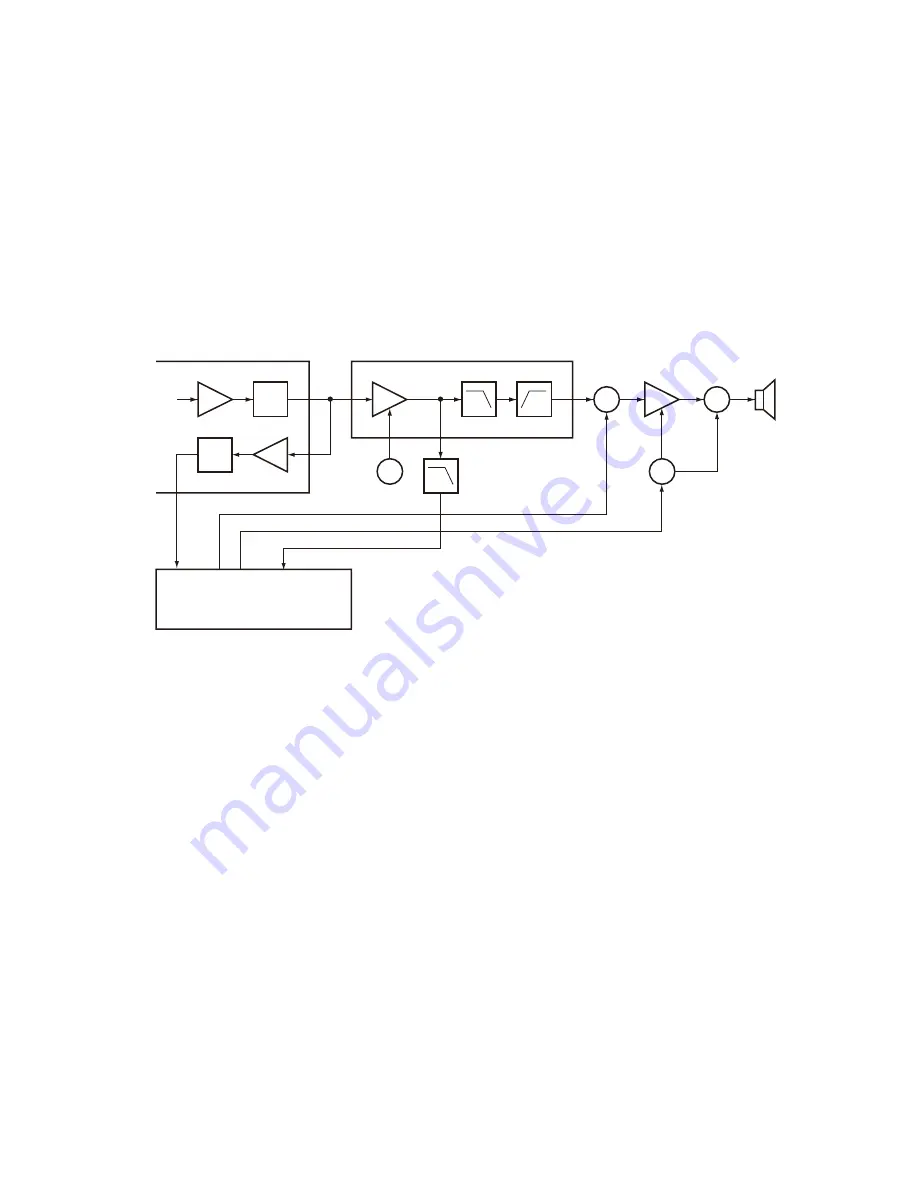

2-5. Squelch

Part of the AF signal from the IC enters the FM IC again,

and the noise component is amplifi ed and rectifi ed by a fi lter

and an amplifi er to produce a DC voltage corresponding to

the noise level.

The DC signal from the FM IC goes to the analog port of

the microprocessor (IC403). IC403 determines whether to

output sounds from the speaker by checking whether the

input voltage is higher or lower than the preset value.

To output sounds from the speaker, IC403 sends a high

signal to the MUTE and AFCO Iines and turns IC302 on

through Q302, Q304, Q305, Q306 and Q307. (See Fig. 3)

2-5. 噪音抑制电路

从 I C200 输出的音频信号的一部分重新进入 I C200,通过

滤波器和放大器将噪音放大和整流并生成一个对应于噪音电

平的直流电压。直流信号进入微处理器的模拟端口 ( I C403)。

IC403 通过检测输入电压是否高于或低于预设值来决定是否通

过扬声器输出声音。

要通过扬声器输出声音,I C403 向静音和自动频率控制振

荡器连线发送一个高电平信号并开启 I C302 通过 Q302, Q304,

Q305,Q306 和 Q307。( 参见图 3)

2-6. Receive signaling

• QT/DQT

300Hz and higher audio frequencies of the output signal

from IF IC are cut by a low-pass fi lter (IC301). The resulting

signal enters the microprocessor (IC403). IC403 determines

whether the QT or DQT matches the preset value, and con-

trols the MUTE and AFCO and the speaker output sounds

according to the squelch results.

3. PLL Frequency Synthesizer

The PLL circuit generates the fi rst local oscillator signal

for reception and the RF signal for transmission.

3-1. PLL

The frequency step of the PLL circuit is 5 or 6.25kHz. A

12.8MHz reference oscillator signal is divided at IC1 by a

fixed counter to produce the 5 or 6.25kHz reference fre-

quency. The voltage controlled oscillator (VCO) output signal

is buffer amplifi ed by Q6, then divided in IC1 by a dual-mod-

ule programmable counter. The divided signal is compared

in phase with the 5 or 6.25kHz reference signal in the phase

comparator in IC1. The output signal from the phase com-

parator is fi ltrered through a low-pass fi lter and passed to

the VCO to control the oscillator frequency. (See Fig. 4)

2-6. 接收信令

•

QT/DQT

来自于中频芯片输出信号的 300H z 和更高的音频被低频

滤波器 ( Q301) 截断。所得到的信号输入微处理器 ( I C403)。

I C403 确定 Q T 或 D Q T 是否匹配预设置,并且根据噪声抑制电

路的结果控制 MUTE 和 AFCO 以及扬声器输出声音。

3. 锁相环频率合成器

锁相环电路生成用于接收的第一本振信号和用于发送的射

频载波信号。

3-1. 锁相环电路

锁相环电路的步进频率为 5 或 6.25k H z。12.8M H z 的参考

振荡器信号通过一个混合计数器在 I C1 中被分频并生成 5 或

6.25k H z 的参考频率。压控振荡器 ( V C O ) 输出的信号通过 Q6

缓冲放大器,然后在 I C1 中被可编程脉冲吞除计数器分频。

被分频的信号在带有 5 或 6.25k H z 参考信号的相位比较器的

IC1 中被比较。从相位比较器输出的信号进入一个低通滤波器

后,并通过压控振荡器来控制振荡频率。( 参见图 4)

Fig. 3 AF amplifi er and Squelch /

图 3 音频放大器和噪音抑制电路

CIRCUIT DESCRIPTION /

电路说明

IC200: FM IF IC

IF AMP

DET

DET

HPF AMP

BUSY

MUTE

AFCO

TI

6

5

67

62

IC301

LPF

QT/DQT

Q303

W/N SW

IC403

MCU

AF AMP

IC300

LPF

HPF

Q302

SW

IC302

AF PA AMP

SP

Q304~Q306

SW

Q307

SW