26

TK-860G/862G

D102,104

Q103

TX VCO

Q106

BUFF

AMP

D101,103

Q101

RX VCO

Q102,

104,105

T/R SW

Charge

pump

LPF

Phase

comparator

1/M

1/N

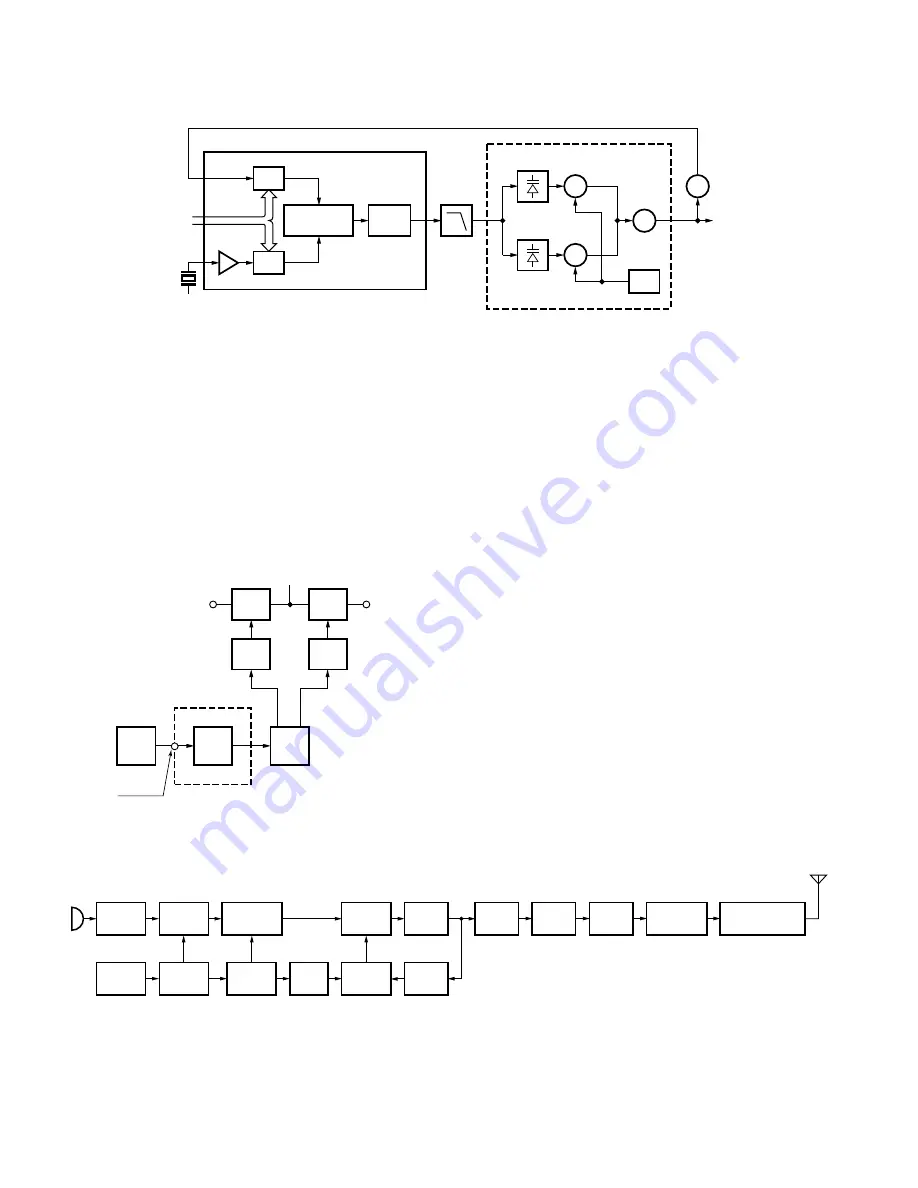

PLL/VCO

5kHz/6.25kHz

5kHz/6.25kHz

REF

OSC

16.8MHz

PLL

DATA

IC3 : PLL IC

Q9

RF AMP

Fig. 6

PLL circuit

■

Unlock Circuit

During reception, the 8RC signal goes high, the 8TC sig-

nal goes low, and Q16 turns on. Q18 turns on and a voltage

is applied to the collector (8R). During transmission, the

8RC signal goes low, the 8TC signal goes high and Q29

turns on. Q28 turns on and a voltage is applied to 8T.

The CPU in the control unit monitors the PLL (IC3) LD

signal directly. When the PLL is unlocked during transmis-

sion, the PLL LD signal goes low. The CPU detects this

signal and makes the 8TC signal low. When the 8TC signal

goes low, no voltage is applied to 8T, and no signal is trans-

mitted.

IC9

SHIFT

REG.

IC502

CPU

Q16

SW

Q18

SW

IC3

PLL

Q29

SW

Q28

SW

LD

CONTORL UNIT

8RC

8C

8R

8T

8TC

PLL lock

: LD "H"

Fig. 7

Unlock circuit

Q22

RF AMP

2SC4093

Q25

RF AMP

2SC3357

Q27

ANT

RF AMP

2SC2954

IC400

POWER AMP

S-AU27AM(K3) : K,M

S-AU27AL(K3) : K3

Q14

BUFFER

2SC5110

(O)

IC508

IC6

Q103

IC507(1/2)

MIC

AF AMP

NJM2904V

MIC KEY

INPUT

AF AMP,

IDC, LPF

TC35453F

IC502

CPU

30622M

4XXXGP

D/A

CONVERTER

M62363FP

IC1

SUM AMP

TA75S01F

X1

VCXO

16.8MHz

VCO

2SK508NV

(K52)

IC3

PLL

MB15A02

Q106

BUFFER

2SC4226

(R24)

Q9

BUFFER

2SC4215

(Y)

Fig. 8

Transmitter system

Transmitter System

■

Outline

The transmitter circuit produces and amplifies the de-

sired frequency directly. It FM-modulates the carrier signal

by means of a varicap diode

■

Power Amplifier Circuit

The transmit output signal from the VCO is amplified to a

specified level of the power module (IC400) by the drive

block (Q22, Q25 and Q27). The amplified signal passes

through the transmission/reception selection diode (D16)

and goes to a low-pass filter. The low-pass filter removes

unwanted high-frequency harmonic components, and the

resulting signal is goes the antenna terminal.

CIRCUIT DESCRIPTION